ECP5 is a great FPGA, it was reversed in Trellis, it’s bigger than ICE40 that was reversed before in icestorm project. And it have lots of cool stuff like

- multipliers

- serdes

- 25klut min (85 max)

- and lots of memory bits

But ECP5 board available on the web are little bit expensive (if you have nothing to do with it ;). Even the OrangeCrab will be about 80$ minimum (but with DDR3 and USB on it).

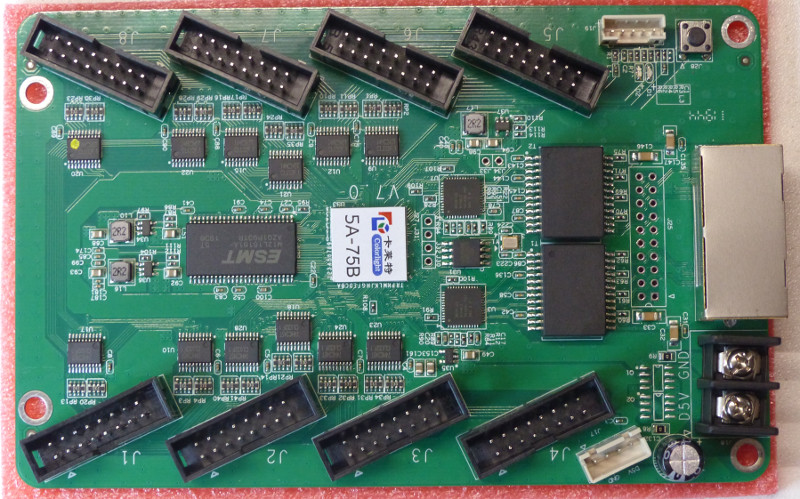

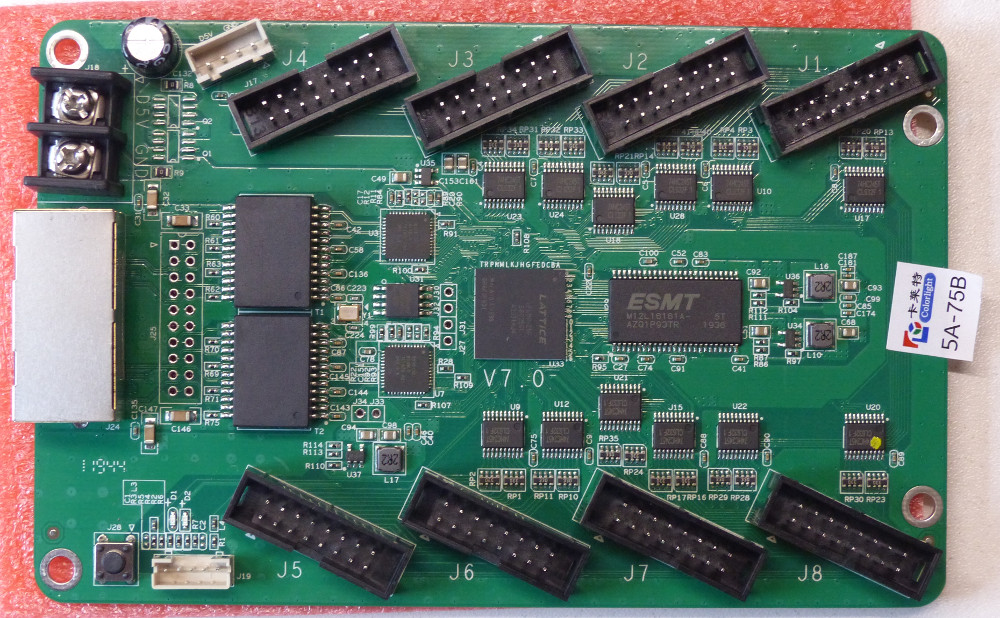

There is a rumor on the web that this leds display board include an ECP5 :

It’s really interesting, because this board cost only $15 ! With the dual SDRAM (M12L16161A) provided and its dual gigabit ethernet phy (Boardcom B50612D B1KMLG). For this low-cost price I order one of course.

I just received it and if we remove the sticker we see a Lattice ECP5 ( LFE5U-25F-6BG256C).

\o/ It’s a really lowcost ECP5 dev kit !

But without schematics. Mike Walter began to reverse it and document the board on its github project.

[Edit 1 March]

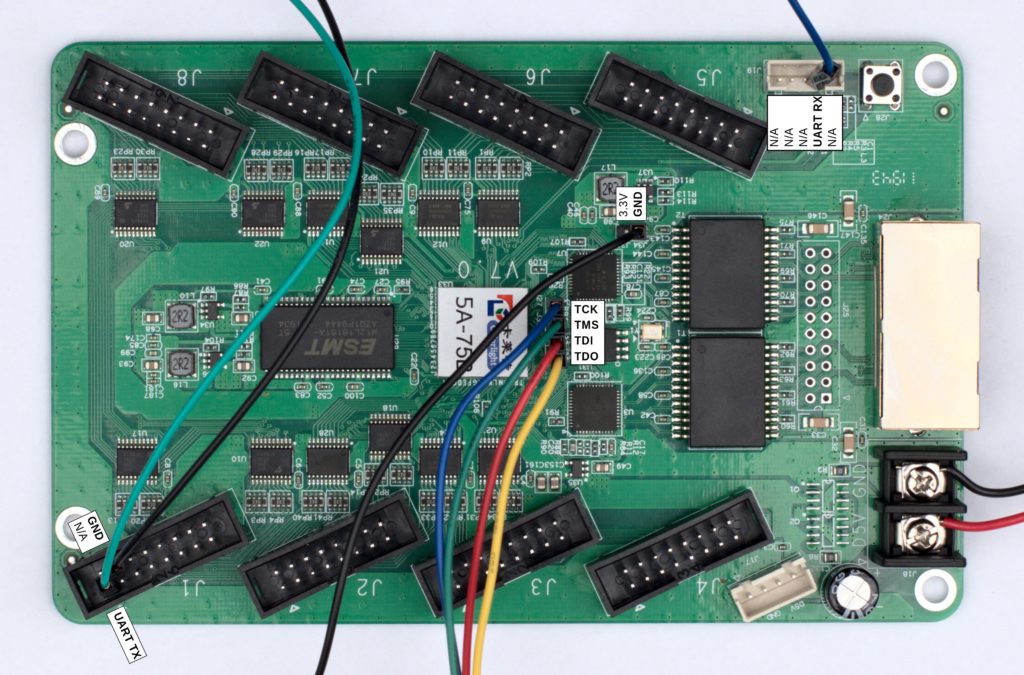

Anton Blanchard give the jtag+uart pinout on its twitter profile :

I configured the FPGA with this adapter from seeedstudio (7.6$), which is a simple FT2232 adapter.

Connect and configure with openFPGALoader

ECP5 is available in openFPGALoader list as we can see :

$ openFPGALoader --list-fpga

IDCode manufacturer family model

0x81113043 lattice ECP5-5G LFE5UM5G-85F-8BG381

0x100381b Gowin GW1N GW1N-4

0x20f30dd altera cyclone 10 LP 10CL025

0x3620093 xilinx spartan7 xc7s15ftgb196-1

0x362d093 xilinx artix a7 35t xc7a35

0x900281b Gowin GW1N GW1N-1

0x1100581b Gowin GW1N GW1NR-9

0x13631093 xilinx artix a7 100t xc7a100

0x41111043 lattice ECP5 LFE5U-25F-6BG256C

0x612bd043 lattice MachXO3LF LCMX03LF-6900C

$ openFPGALoader -cdigilent --detect

idcode 0x41111043

manufacturer lattice

model LFE5U-25F-6BG256C

family ECP5

Open source synthesize and place&route tools

We can then load a simple blinker bitstream with openFPGALoader. But first, we have to synthesize one. Trabucayre gave me a simple blinker project I added to the BLP (Blinking Led Project).

This project require yosys, nextpnr and trellis to be installed. Installations instructions are given on trellis repository.

$ git clone --recursive https://github.com/SymbiFlow/prjtrellis

$ cd prjtrellis/libtrellis

$ cmake -DCMAKE_INSTALL_PREFIX=/usr .

$ make

$ sudo make installThen for next-pnr:

$ git clone https://github.com/YosysHQ/nextpnr.git

$ cd nextpnr

$ cmake -DARCH=ecp5 -DTRELLIS_INSTALL_PREFIX=/usr/ .

$ make

$ sudo make install

And finally Yosys

$ git clone https://github.com/YosysHQ/yosys

$ cd yosys

$ make

$ sudo make installSynthesize blinker

The blinker projet can be found on this github repository :

$ git clone https://github.com/Martoni/blp.git

$ cd blp/platforms/colorlight/

$ make

...

ecppack --svf blink.svf blink_out.config blink.bitThen, once JTAG is plugged we can download it with openFPGALoader :

$ openFPGALoader -cdigilent blink.bit

Open file blink.bit DONE

Parse file DONE

Enable configuration: DONE

SRAM erase: DONE

Loading: [==================================================] 100.000000%

Done

Disable configuration: DONEAnd see the orange LED blinking !

Some links

[this article will be edited as I progress]

HI,

very nice article for starting with colorlight board.

I followed it trough but when I get to downloading the blinker project to FPGA I get this problem:

DirtyJTAG probe limited to 600kHz

Open file blink.bit DONE

Parse file DONE

Enable configuration: FAIL

displayReadReg

Config Target Selection : 0

Done Flag

Std PreAmble

SPIm Fail1

No err

Do you know what could be the problem?

Regards

Hi Filip,

Your problem seems to come from a bug in openFPGALoader.

Bug that has just been fixed.

You should clone the last git head of openFPGALoader and test it.

Tell me if it’s ok.

It works! Thank you so much!

Now I’m able to develop FPGA with 17$ hardware (15$ board and 2$ JTAG cable) 🙂

\o/

Can you give a reference for your 2$ JTAG cable please ?

It is 2$ bluepill STM32 board with DirtyJTAG firmware:

https://github.com/jeanthom/DirtyJTAG

Hello,

I have an issue with the Colorlight:

Info: [ 37376, 38679) |***********ecppack --svf blink.svf blink_out.config blink.bit

seb@seb-MINT ~/blp/platforms/colorlight $ openFPGALoader -cdigilent blink.bit

Error: device a0911043 not supported

The board is correctly detected but model changes a bit:

$ openFPGALoader -cdigilent --detectidcode 0x41111043

manufacturer lattice

model LFE5U-25

family ECP5

$ openFPGALoader -b colorlight -cdigilent /home/seb/simpleButton.bitBoard colorlight has not default cable

Unknown device family

terminate called after throwing an instance of 'std::exception'

what(): std::exception

Aborted

Could you please help me?

Thank you a lot.

If you try without «-b colorlight» option ?

$ openFPGALoader -cdigilent /home/seb/simpleButton.bit

Unknown device family

terminate called after throwing an instance of ‘std::exception’

what(): std::exception

Aborted

Allways the unknown device familly issue

Tested on Ubuntu 20.10 and same result:

seb@seb-PC:~/blp/platforms/colorlight$ openFPGALoader -cdigilent blink.bit

Unknown device family

terminate called after throwing an instance of ‘std::exception’

what(): std::exception

Abandon (core dumped)

seb@seb-PC:~/blp/platforms/colorlight$ openFPGALoader -cdigilent –detect

idcode 0x41111043

manufacturer lattice

model LFE5U-25

family ECP5

Could you try with -v option to have more informations and check physical JTAG connection?

Which JTAG probe you use?

Hello,

Here with the -v option:

seb@seb-PC:~/blp/platforms/colorlight$ openFPGALoader -v -cdigilent simpleButton.bit

found 1 devices

idcode 0x41111043

manufacturer lattice

model LFE5U-25

family ECP5

File type : bit

Unknown device family

terminate called after throwing an instance of ‘std::exception’

what(): std::exception

Abandon (core dumped)

Sipeed usb jtag to TTL from seeedstudio

https://scontent-lhr8-2.xx.fbcdn.net/v/t1.0-9/144306228_10158074383133348_5992723884657304088_o.jpg?_nc_cat=105&ccb=2&_nc_sid=0debeb&_nc_ohc=E_dEpXOH_bgAX8wpYr5&_nc_ht=scontent-lhr8-2.xx&oh=bf6e2914af1b84041f5395502bf9b15f&oe=60398E44

the FPGA is warming a bit like 40°C to 50°C when powerred on, is this normal?

Hello Fabien,

Nice article thank you!

I’ve got trouble to load the colorlight with an dirtyJTAG cable ;

~/blp/platforms/colorlight$ openFPGALoader -cdirtyJtag -v blink.bit

DirtyJTAG probe limited to 600kHz

found 1 devices

idcode 0x41111043

manufacturer lattice

model LFE5U-25

family ECP5

File type : bit

Open file blink.bit DONE

Parse file DONE

Lattice bitstream header infos

Part: LFE5U-25F-6CABGA256

IDCode : 41111043

displayReadReg

Config Target Selection : 0

Std PreAmble

CRC ERR

EXEC Error

Enable configuration: DONE

SRAM erase: DONE

Loading: [==================================================] 100.000000%

Fail

displayReadReg

Config Target Selection : 0

JTAG Active

ISC Enable

Write Enable

Read Enable

Std PreAmble

CRC ERR

EXEC Error

Any hint?

Ok, I figure out what was wrong… the colorlight board was powered with an external power supply (+5vcc) so I figured that I didn’t need to power the JTAG pin j33 with 3.3v. I was wrong!

[From admin: comments have problems, here a message from Alexander Bleitner]

Thank you for the comment. I was having the same issue!

Before connecting 3v3 as well I got the error:

$ openFPGALoader -cft2232 blink.bit -v

empty

Can't read iSerialNumber field from FTDI: considered as empty string

Jtag frequency : requested 6.00MHz -> real 6.00MHz

found 1 devices

index 0:

idcode 0x41111043

manufacturer lattice

family ECP5

model LFE5U-25

irlength 8

File type : bit

Open file: DONE

b3bdffff

Parse file: DONE

bitstream header infos

Part: LFE5U-25F-6CABGA256

idcode: 41111043

mismatch between target's idcode and bitstream idcode

bitstream has 0x41111043 hardware requires 0xffffffc3

Error: Failed to program FPGA: std::exception

$

and with openocd instead of openFPGAloader

$ openocd -f colorlight.cfg

Open On-Chip Debugger 0.11.0

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : clock speed 25000 kHz

Info : JTAG tap: ecp5.tap tap/device found: 0x41111043 (mfg: 0x021 (Lattice Semi.), part: 0x1111, ver: 0x4)

Warn : gdb services need one or more targets defined

svf processing file: "blink.svf"

95% Error: tdo check error at line 17

Error: READ = 0xffffffc3

Error: WANT = 0x41111043

Error: MASK = 0xffffffff

Time used: 0m0s446ms

svf file programmed failed

$

This log might help other people find the solution

Best Regards from across the Rhine,