Found on the web:

Found on the web:

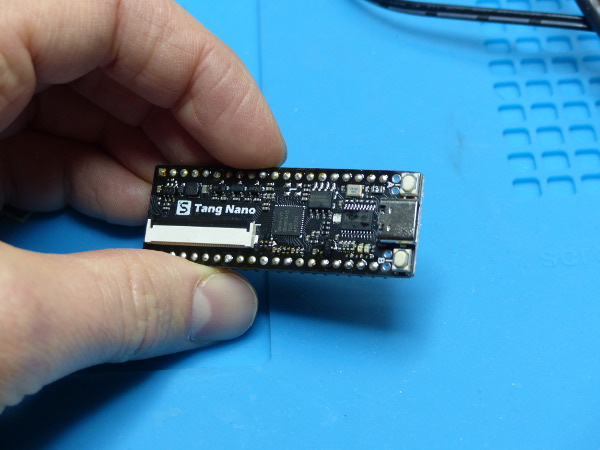

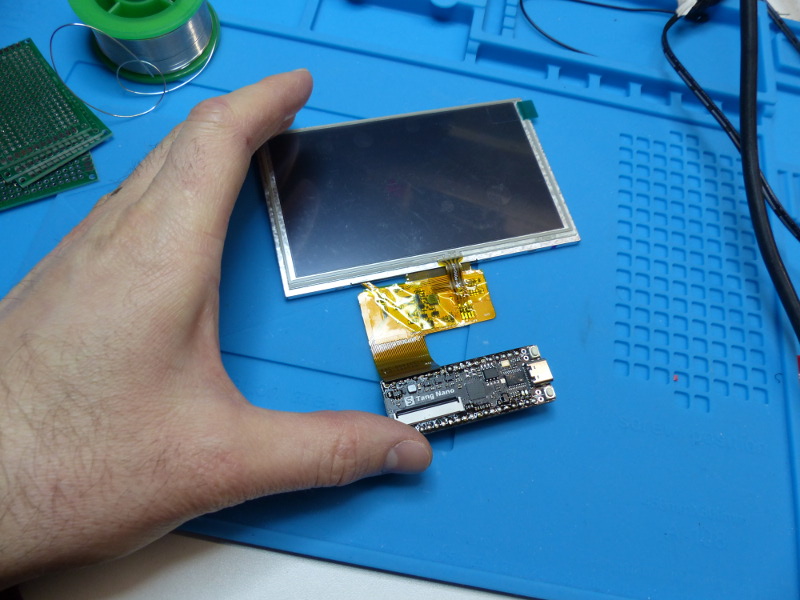

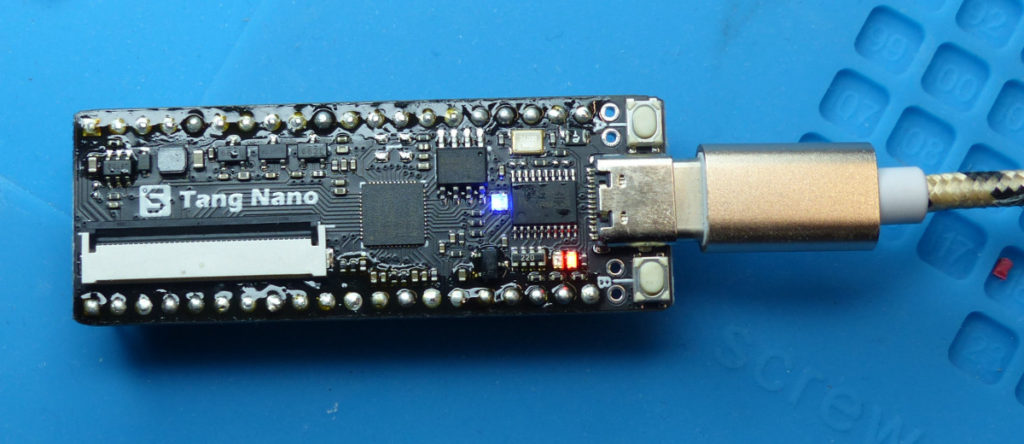

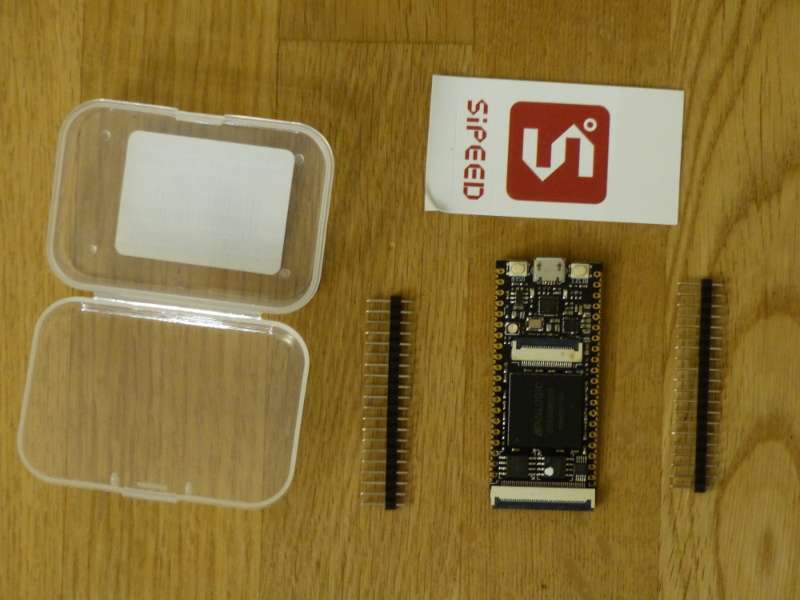

Sipeed continue dans sa course à l’échalote des kit FPGA low cost en proposant un kit Gowin à $4.90. Évidemment à ce prix là c’était trop tentant d’en prendre un. Bon en vrai vu que les frais de port ne sont pas négligeable j’ai également pris l’écran proposé et je m’en suis finalement sortie pour une vingtaine d’€. Ce qui reste néanmoins raisonnable.

Le kit est fourni avec des headers males (pattes) non soudés. Ils ne sont pas nécessaire pour faire clignoter la LED ou pour jouer avec l’écran, mais c’est quand même utile.

Premier boulot en recevant le truc donc : souder les headers.

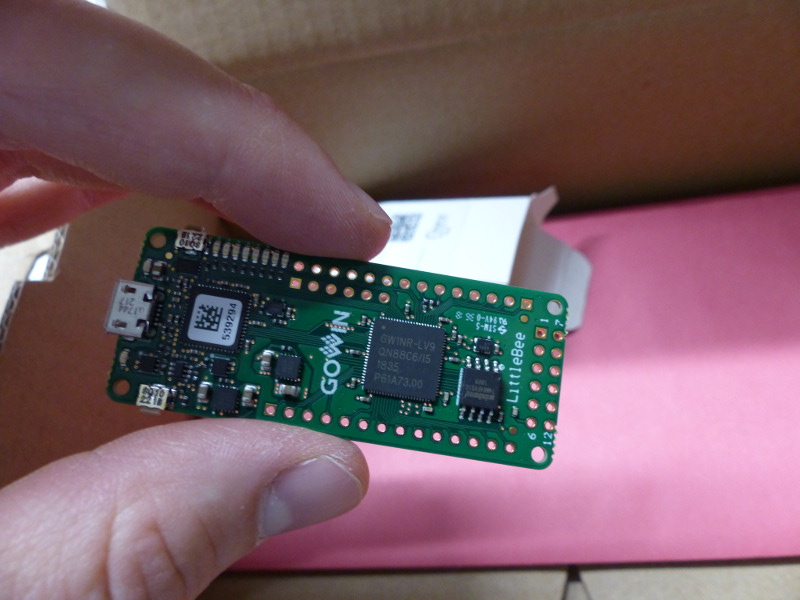

Le FPGA soudé sur la carte est un GW1N-LV1, assez petit donc, mais il reste raisonnable puisque de la même taille que le ice40 soudé sur le icestick. C’est d’ailleurs le kit utilisé actuellement par Pepijn de Vos son projet d’ingénierie inverse nommé Apicula (mais chuuut le projet n’est pas encore public !).

Le branchement se fait au moyen d’un câble USB-C non fourni. Au premier branchement, la LED rouge qui semble être celle de l’alimentation s’allume et la led RGB du centre se met à clignoter en allumant les trois couleurs à la suite.

Les messages noyau m’affichent le traditionnel double tty typique d’un convertisseur USB-Série habituel (CH552T, un microcontrôleur chinois):

$ sudo dmesg -c

[365812.686837] usb 3-2: new full-speed USB device number 25 using xhci_hcd

[365812.838484] usb 3-2: New USB device found, idVendor=0403, idProduct=6010, bcdDevice= 5.00

[365812.838490] usb 3-2: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[365812.838492] usb 3-2: Product: Sipeed-Debug

[365812.838494] usb 3-2: Manufacturer: Kongou Hikari

[365812.838496] usb 3-2: SerialNumber: 85522A1A47

[365812.840468] ftdi_sio 3-2:1.0: FTDI USB Serial Device converter detected

[365812.840534] usb 3-2: Detected FT2232C

[365812.841192] usb 3-2: FTDI USB Serial Device converter now attached to ttyUSB0

[365812.841373] ftdi_sio 3-2:1.1: FTDI USB Serial Device converter detected

[365812.841427] usb 3-2: Detected FT2232C

[365812.841727] usb 3-2: FTDI USB Serial Device converter now attached to ttyUSB1

On remarquera que cette fois le numéro de série n’est pas en chinois 😉

La connexion au ttyUSB0 (en 115200) fournie un echo du clavier un peu bizarre :

�n�a�u�r�s�i�t�e�n�a�s�u�t�i�e�n�a�s�u�t�i�e�n�s�a�u�t�i�e�n�r�a�s�u�t�i�e�n�r�s�a�u�t�i�e�n�r�s�a�t�u�i�eEt le ttyUSB1 semble ne pas «fonctionner».

Il est fort probable que le kit soit entièrement utilisable avec des logiciels libre à Noël lors de la grand messe allemande : le Chaos Communication Congress à Liepnitz.

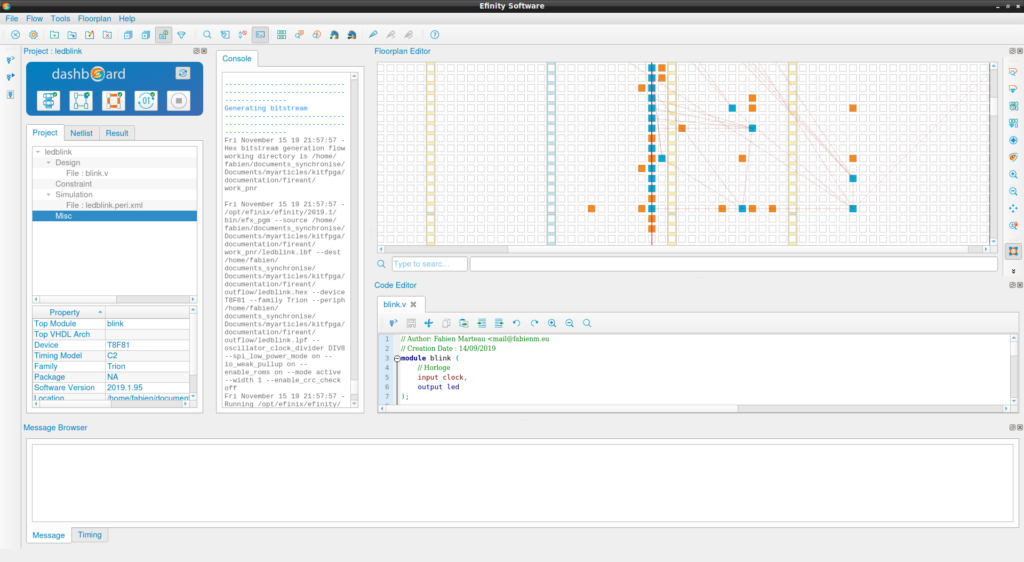

Pour le moment nous allons nous contenter de l’IDE chinois fourni, que j’avais déjà installé pour le little bee. Pour le code, il y a des exemples fournis sur le github de sipeed. Pour la documentation c’est par ici. Et comme d’habitude avec les trucs chinois, quand la doc en anglais semble trop limitée, ne pas hésiter à aller faire un tour sur la version chinoise à coup de google traduction.

Si le floorplanning ne veut pas se lancer c’est qu’il faut bien configurer sa variable LD_LIBRARY_PATH avant de lancer l’appli:

$ export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:/home/flf/myapp/gowin/IDE/lib

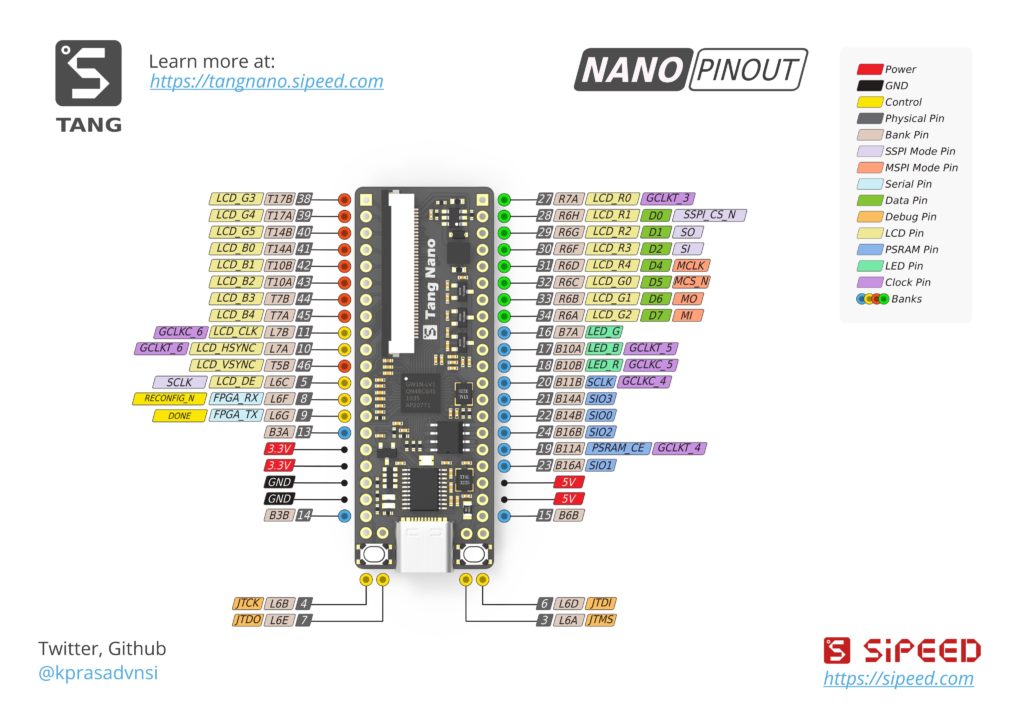

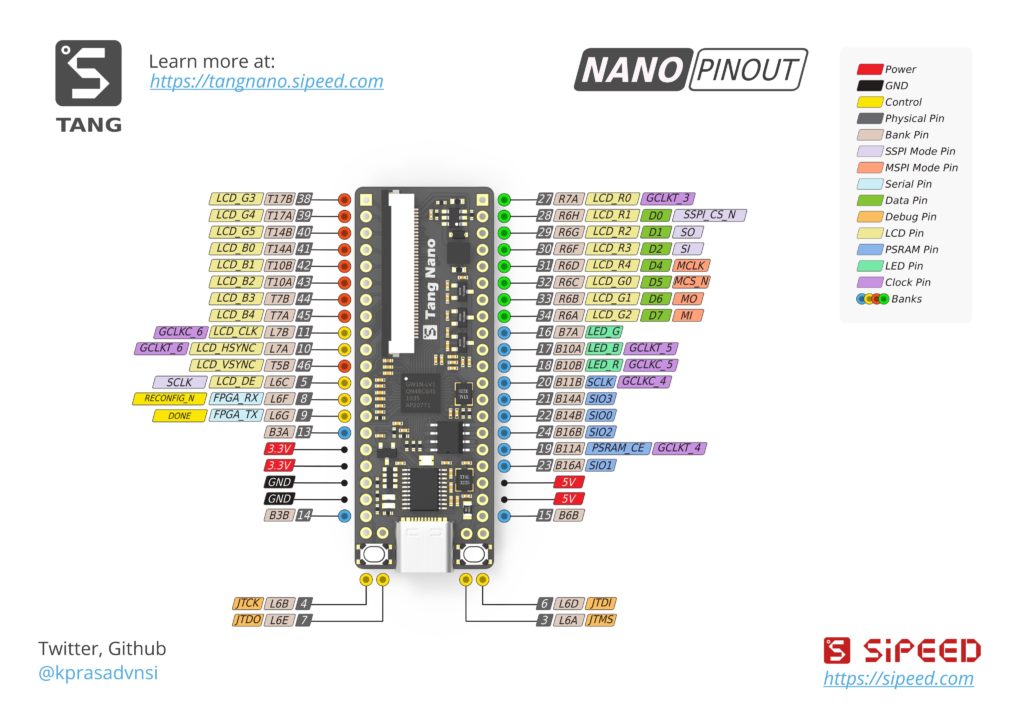

$ ./gw_ide -gui– Nano board pinout (blog)

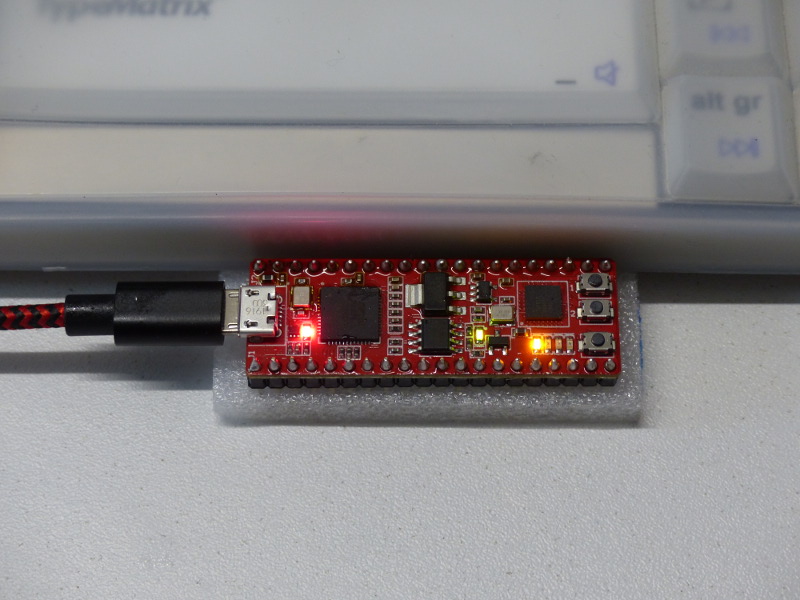

J’en avait déjà parlé dans les colonnes de ce blog. Une nouvelle société produit un FPGA nommé Trion T8. Ce FPGA est la base d’une petite carte de développement proposée par les HongKongais de XIPS Technology sur le site crowdsupply.

Évidemment je n’ai pas résisté à participer à la campagne. Quelques manifestations à HongKong et quelques déboire avec Fedex puis Mondial Relais, voici enfin le kit tant attendu arrivé chez moi.

Le kit est arrivé dans un énorme carton, mais c’est presque habituel dans ce genre de cas. J’avais pris sans les headers soudés mais ils sont tout de même fournis. J’ai juste eu à les souder moi même.

Au branchement une led rouge qui semble être celle de l’alimentation s’allume. Les 4 LED oranges se mettent elles à compter en binaire.

Dans les messages noyau nous avons la traditionnelle interface ttyUSB0 du FTDI :

$ dmesg

[97997.987953] usb 3-1: USB disconnect, device number 11

[97997.988359] ftdi_sio ttyUSB0: FTDI USB Serial Device converter now disconnected from ttyUSB0

[97997.988397] ftdi_sio 3-1:1.0: device disconnected

[98000.296737] usb 3-1: new high-speed USB device number 12 using xhci_hcd

[98000.445226] usb 3-1: New USB device found, idVendor=0403, idProduct=6014, bcdDevice= 9.00

[98000.445231] usb 3-1: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[98000.445233] usb 3-1: Product: Single RS232-HS

[98000.445235] usb 3-1: Manufacturer: FTDI

[98000.446052] ftdi_sio 3-1:1.0: FTDI USB Serial Device converter detected

[98000.446118] usb 3-1: Detected FT232H

[98000.446278] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB0

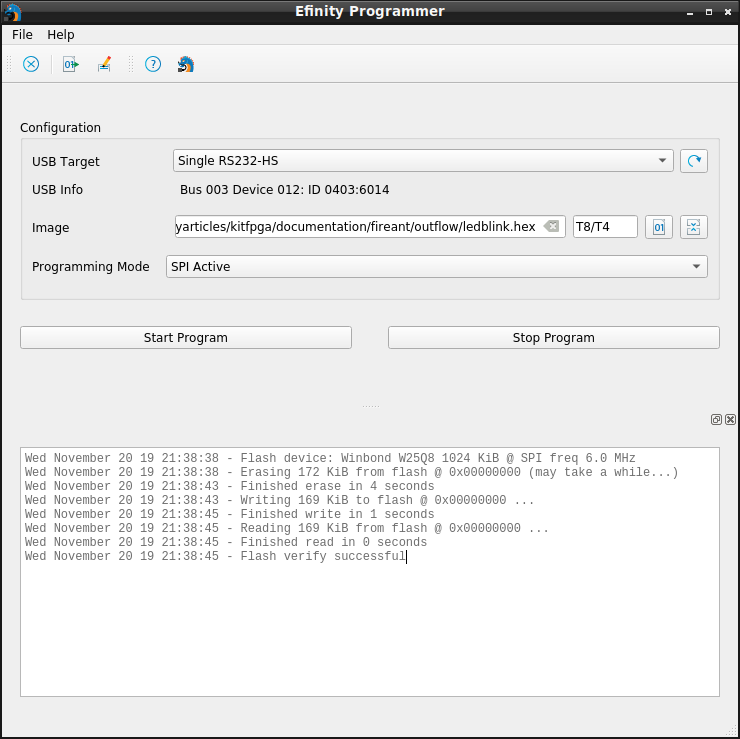

J’avais déjà reçu la license de la part de Efinix et Xips technology, du coup mon blinking led design était près à télécharger. Le bitstream est au format *.hex et se flash super facilement avec le Efinity programmer (tools -> programmer).

Par contre ma led ne clignote pas, je pense avoir encore quelques soucis avec les configs d’I/O et de PLL pour l’instant. Je doit encore me former à l’Efinity Interface Designer de Efinix qui est assez déroutant par rapport aux autres IDE.

Il est possible de charger le bitstream avec openFPGALoader sans problème de nos jours :

$ openFPGALoader -b fireant counter/outflow/counter.hex

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file DONE

Detail:

Jedec ID : ef

memory type : 40

memory capacity : 14

00

Detail:

Jedec ID : ef

memory type : 40

memory capacity : 14

flash chip unknown: use basic protection detection

Erasing: [==================================================] 100.00%

Done

Writing: [==================================================] 100.00%

Done

Wait for CDONE DONE

[ToBeEdited]

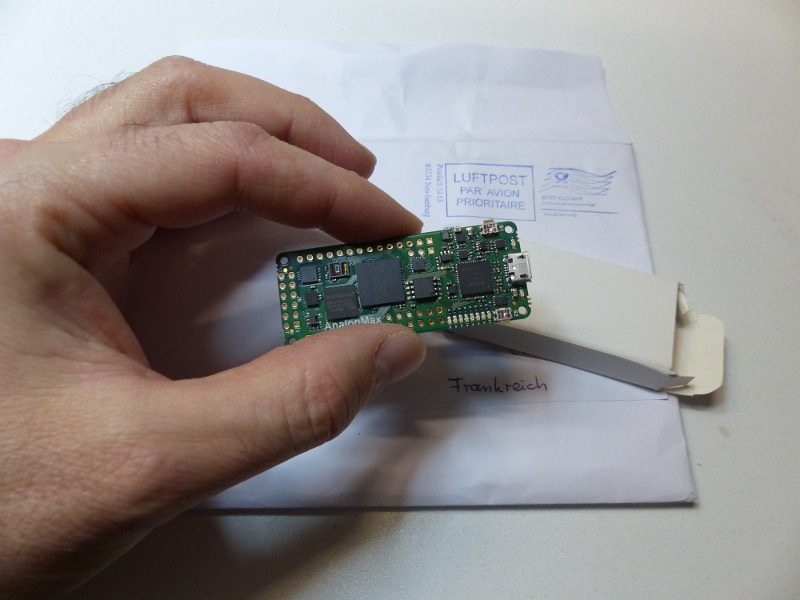

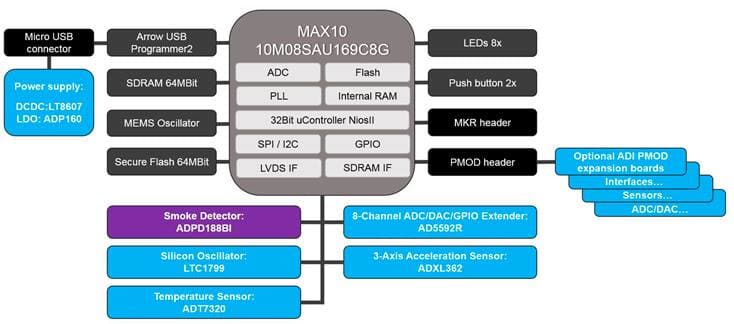

Arrow propose un kit de développement nommé AnalogMax pour 80$ environ. L’entreprise qui fabrique la carte est Trenz Electronic qui réalise également le kit gowin.

Le FPGA est relativement gros et la carte possède un certain nombre de périphérique analogiques sympathique comme un détecteur de fumée, un capteur de température, quelque canaux ADC et DAC ainsi que des GPIO.

Au branchement du kit sur l’usb on a juste la led verte allumée. L’appuie sur le bouton à droite allume une des huit leds de la rangée, et l’appui sur l’autre bouton allume l’autre led rouge et inscrit un message sur l’uart (115200):

UHSA R1.0

[TO BE EDITED]

Oui je sais c’est nul 😉

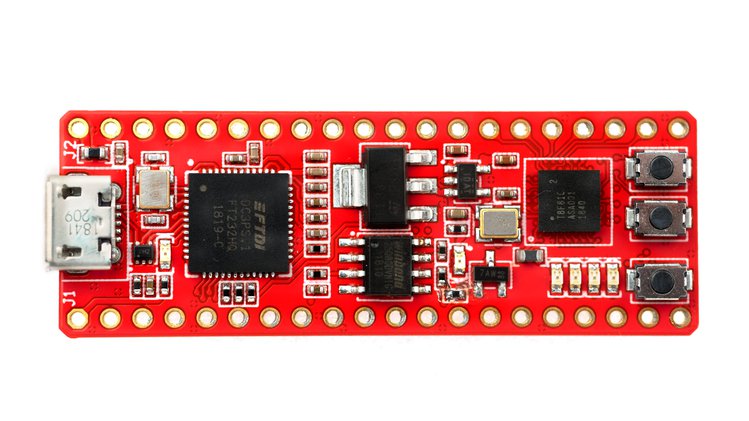

Je viens donc de recevoir ma carte petite abeille (littlebee) munie d’un FPGA du chinois GOWIN.

La carte produite et vendue par la société allemande Trenz Electronic permet de se faire la main avec le composant pour moins de 40€ (un peu plus avec les frais de ports UPS …).

Branchement

Au branchement à la sortie du carton les huit leds rouge s’allument ainsi qu’une led verte que je suppose de «power».

Les messages noyau nous donnent deux ports séries ttyUSBx :

$ dmesg

[630417.919258] usb 3-1: new high-speed USB device number 35 using xhci_hcd

[630418.059577] usb 3-1: New USB device found, idVendor=0403, idProduct=6010

[630418.059581] usb 3-1: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[630418.059583] usb 3-1: Product: Dual RS232-HS

[630418.059584] usb 3-1: Manufacturer: FTDI

[630418.060116] ftdi_sio 3-1:1.0: FTDI USB Serial Device converter detected

[630418.060155] usb 3-1: Detected FT2232H

[630418.060352] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB0

[630418.060499] ftdi_sio 3-1:1.1: FTDI USB Serial Device converter detected

[630418.060528] usb 3-1: Detected FT2232H

[630418.060648] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB1

Si on se connecte au port série ttyUSB1 on obtient un affichage de la résolution du problème des philosophes.

Philosopher 0 [P: 3] THINKING [ 750 ms ]

Philosopher 1 [P: 2] HOLDING ONE FORK

Philosopher 2 [P: 1] EATING [ 450 ms ]

Philosopher 3 [P: 0] STARVING nabled

Philosopher 4 [C:-1] HOLDING ONE FORK get back,

Philosopher 5 [C:-2] EATING [ 375 ms ]

Il est probable que nous ayons ici un RISC-V dans le tiroir.

La connexion d’un terminal sur le port ttyUSB0 ne donne rien par contre.

IDE

Voila pour le déballage, maintenant il va falloir installer les outils pour faire clignoter ces leds !

[To Be Edited …]

FireAnt est un kit de développement «de la taille d’un pouce» concu par la société Xips Technology et permettant de se faire la main sur le FPGA Trion T8 de la société Efinix.

Le kit est en crowdsourcing sur la plate-forme crowdsupply pour $30.

Pour ce prix on a le droit à :

Efinix est une toute nouvelle société qui propose des petits FPGA gravés en 40nm. Pour les tout petits FPGA de leur gamme, la société propose ce qu’elle appelle un MPM pour «Mask Programmable Memory» -> la possibilité de figer le design en usine et de ne plus avoir à configurer le FPGA à chaque démarrage.

Un IDE permettant de faire la synthèse, le placement-routage et le bitstream est fourni «gratuitement». À condition de posséder un kit de développement (J’ai beau négocier, ils ne veulent pas me le donner tant que je n’aurais pas reçu le kit 😉 ).

Bref, il n’est pas encore question d’outils libres pour ces FPGA pour l’instant. Cependant, ça fait du bien de voir de nouveaux acteurs dans le domaine des FPGA «physique».

Wavedrom est un outils magique pour générer de très beaux chronogrammes à partir d’une base texte (JSON). Il existe un outils en ligne de commande pour générer des rendu en SVG ou PNG. Cependant, Wavedrom reste très lié au web, pas facile de l’intégrer dans un document wysiwyg comme libreoffice.

On peut bien sûr générer l’image puis l’intégrer à son document, mais cela éparpille très vite le nombre de fichiers source à gérer. Or, un des intérêt d’un document libreoffice est d’inclure toute les sources permettant de générer et modifier le document.

L’idéal serait d’avoir un plugin Libreoffice pour wavedrom, mais pour l’instant cela n’existe pas.

Krispy propose une solution/hack sur la mailing list de wavedrom.

Cette solution nécessite d’avoir un accès web et de faire son chronograme avec l’éditeur en ligne de wavedrom. Cet éditeur permet de «stocker» la description du chronograme dans l’URL. Il suffit pour cela de cliquer sur le menu sandwich en bas à droite et de sélectionner «expand url» pour avoir le contenu du chronogramme dans l’url comme ceci.

Il n’est pas utile de comprendre ce qui est écrit dans l’url, il suffit de cliquer dessus pour avoir le texte «lisible».

Pour l’intégrer à son document libreoffice il suffit de:

De cette manière, le source du chronogramme est bien embarqué dans le document. Il faudra certe refaire une manip légèrement fastidieuse à chaque modification, mais nous avons tout de même une solution viable.

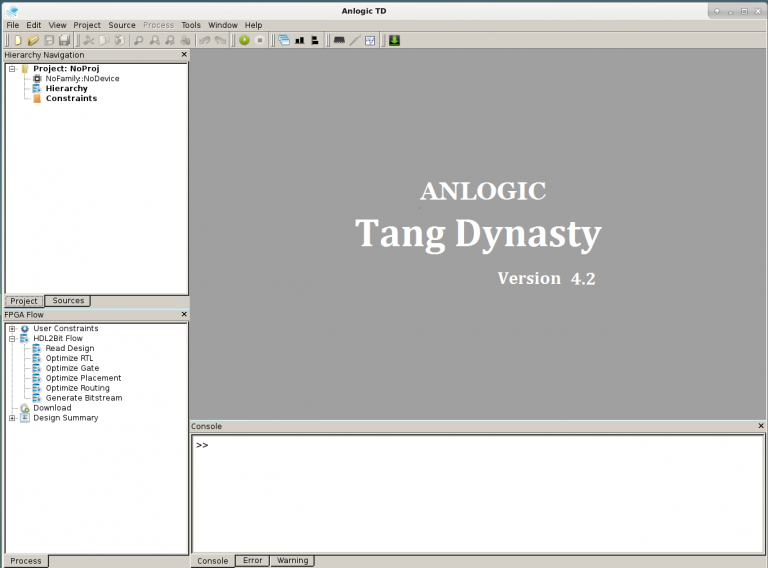

La société chinoise SiPeed propose un kit de développement permettant d’évaluer le FPGA chinois EG4S20BG256 produit par Anlogic. Le kit peut être commandé pour une vingtaine de dollars sur le site de vente en ligne Seeed spécialisé dans les kits de développement en électronique «grand public».

Au branchement du kit Debian/Linux détecte un convertisseur USB-JTAG de chez Anlogic:

$ sudo dmesg -c

[30017.300586] usb 3-2: new full-speed USB device number 5 using xhci_hcd

[30017.441796] usb 3-2: New USB device found, idVendor=0547, idProduct=1002

[30017.441801] usb 3-2: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[30017.441804] usb 3-2: Product: USB-JTAG-Cable

[30017.441807] usb 3-2: Manufacturer: Anlogic

L’environnement de développement est disponible en téléchargement (~100Mo) sous forme d’une archive rar ici. Le fichier se décompresse avec la commande unrar:

$ unrar x ../TD_RELEASE_SEPTEMBER2018_RHEL.rar

Il faut ensuite mettre en exécutable le répertoire bin:

$ chmod +x bin/*

Et on peut ensuite lancer l’IDE:

$ cd bin ; ./td -gui

La fenêtre suivante s’ouvre alors :

C’est l’environement de développement le plus simple à installer que j’ai pu voir depuis que je bricole des FPGA. Même si la procédure d’installation est quand même étrange (un obscure .rar à télécharger puis à décompresser).

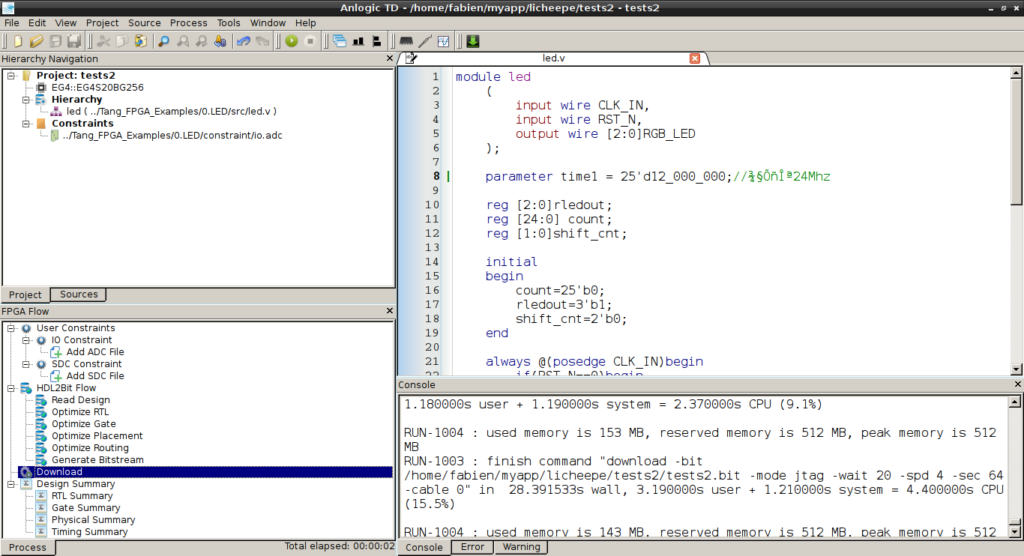

Pour synthétiser un premier design on va avoir besoin d’un minimum de documentation sur la schématique de la carte ainsi que sur le pinout du FPGA. On trouvera les schémas du kit en format pdf ici.

On trouve des exemples de code pour le kit sur github, notamment pour faire clignoter une led. La base du Hello World en électronique.

Pour tester la led qui clignote on crée un nouveau projet avec le fpga EG4S20BG256. On ajoute ensuite le source pour la led se trouvant dans le répertoire Tang_FPGA_Examples/0.LED/src/led.v

L’extension du fichiers de contrainte est en *.adc pour l’exemple de led le fichier se trouve dans le répertoire Tang_FPGA_Examples/0.LED/constraint/io.adc

Une fois les deux fichiers ci-dessus ajouté à notre projet on peut lancer la procédure complète pour générer le bitstream en double-cliquant sur l’icône «Generate Bitstream» dans l’encart «FPGA Flow» de l’ide.

La génération du bitstream est très rapide. Pour le télécharger ensuite dans le FPGA il faut bien sûr que le kit soit connecté à l’usb.

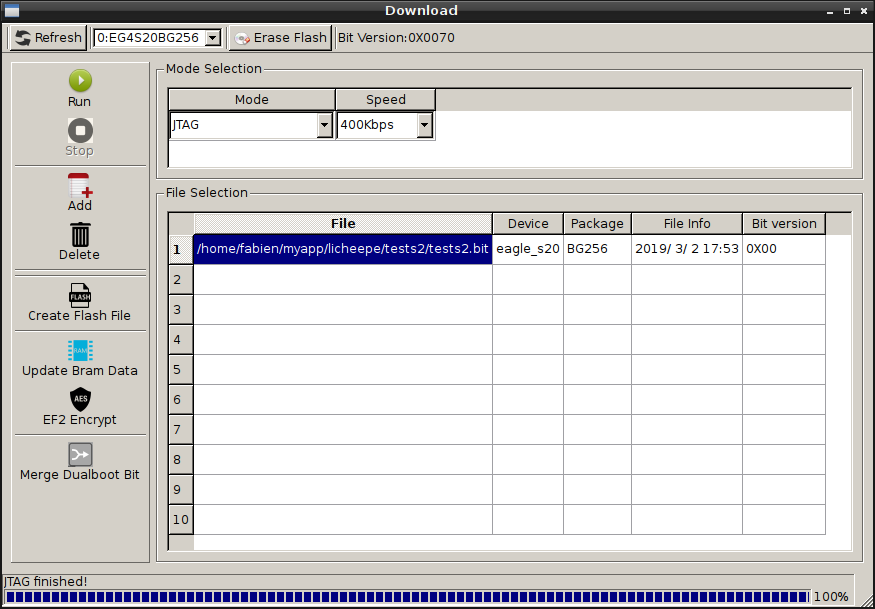

Le configurateur se lance en allant dans le menu Tools -> Download.

Chez moi j’ai du lancer l’ide en sudo pour éviter un plantage fatal, à ce moment. Le configurateur se présente comme ci-dessous :

Il faut ajouter le fichier bitstream au moyen du bouton de gauche «Add» puis cliquer sur la ligne du tableur pour «dégriser» le bouton «run», qui permet de télécharger le bitstream pour configurer le FPGA.

Pour conclure, je pensais beaucoup plus souffrir à mettre en route ce kit à la documentation majoritairement en chinois. Mais la note de blog de JAEB et le projet d’exemples sur github m’ont beaucoup aidé à faire clignoter cette led tricolore rapidement. À l’avenir il faudra regarder si ce FPGA est vraiment nouveau ou si ça n’est pas une copie d’un constructeur bien connu. On doit pouvoir vérifier ça avec le bitstream généré.

Au bout de quelques temps, la licence du logiciel expire. Il n’est plus possible de synthétiser avec. Un site chinois donne le truc pour que ça remarche. Pour éviter ce piratage, il semble être maintenant possible d’utiliser Yosys pour la partie synthèse !

This is just an install success story of Libero on Debian 9 (stretch). For the Risc-V contest, I recently acquired the Microsemi IGLOO2 development kit named FUTUREM2GL-EVB distributed by Futur-Electronic.

The development software for the IGLOO2 is named Libero and according to Microsemi, should works on Linux. But officially support only RedHat, CentOS and SuSE … not Debian. Microsemi provide a Linux installation guide to install it. It’s useful but should be adapted for Debian.

Download and install Libero

The first thinks to do is to download the installing file for Linux (and not the SP1 file which is only an update). Once downloaded we just have to launch it, if it’s not executable we can change rights with chmod command.

$ chmod 666 Libero_SoC_v11.9_Linux.bin $ ./Libero_SoC_v11.9_Linux.bin

An install windows will raise and we can follow directives.

Licensing

Once installed, we need to install the license. For that, we need to know our mac address :

$ ip addr show dev eth0 [...] link/ether 12:34:56:78:9a:bc [...]

The key that should be given to Microsemi is in upper case without ‘:’ :

$ ipython

In [1]: "12:34:56:78:9a:bc".replace(':','').upper()

Out[1]: '123456789ABC'

With this key we can then ask for a license file on microsemi website. The official Linux guide talk about license.dat file, but for me it was license.zip … Both are zip file in fact. We can then unflat it with unzip command:

$ unzip License.zip Archive: License.zip inflating: License.dat

The unflated file is a text file that should be edited with you text edito as explained in guide (page 6).

License server

The license server deamon must be downoaded on official microsemi website. Choose «Linux deamon» in table. It’s an archive of several binaries that should be unflated :

$ cd $ tar -zxvf Linux_Licensing_Daemon.tar.gz Linux_Licensing_Daemon/ Linux_Licensing_Daemon/actlmgrd Linux_Licensing_Daemon/lmgrd Linux_Licensing_Daemon/lmhostid Linux_Licensing_Daemon/lmutil Linux_Licensing_Daemon/mgcld Linux_Licensing_Daemon/snpslmd Linux_Licensing_Daemon/syncad Linux_Licensing_Daemon/synplctyd

Export shell variables

Before launching software, we have to export some paths in our .bashrc :

#Libero LIBERO_LICENSE_FOLDER=/home/giselle/flexlm LD_LIBRARY_PATH=/usr/lib/i386-linux-gnu/:/usr/lib/x86_64-linux-gnu/ # For Floating License from a License Server export LM_LICENSE_FILE=1702@gisellelaptop:$LM_LICENSE_FILE export SNPSLMD_LICENSE_FILE=1702@gisellelaptop:$SNPSLMD_LICENSE_FILE # <1702> is the port number # martonilp is the license server host name #For Node-Locked License export LM_LICENSE_FILE=$LIBERO_LICENSE_FOLDER/license.dat:$LM_LICENSE_FILE export SNPSLMD_LICENSE_FILE=$LIBERO_LICENSE_FOLDER/license.dat:$SNPSLMD_LICENSE_FILE export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:/usr/lib export DISPLAY=:0 export PATH=/opt/microsemi/Libero_SoC_v11.9/Libero/bin:$PATH

On my computer, Microsemi softwares are installed in /opt/ directory.

Launching Libero

First launch license server :

$ cd $./flexlm/lmgrd -c ~/flexlm/License.dat -log /tmp/lmgrd.log

Once license server launched we can run Libero :

$ libero /opt/microsemi/Libero_SoC_v11.9/Libero/bin/libero_bin: /opt/microsemi/Libero_SoC_v11.9/Libero/lib/libz.so.1: no version information available (required by /usr/lib/i386-linux-gnu/libpng16.so.16)

I had a little problem with libz provided with libero package, then I removed it and linked libz of my distribution :

$ apt-file search libz.so lib32z1: /usr/lib32/libz.so.1 lib32z1: /usr/lib32/libz.so.1.2.8 lib32z1-dev: /usr/lib32/libz.so zlib1g: /lib/x86_64-linux-gnu/libz.so.1 zlib1g: /lib/x86_64-linux-gnu/libz.so.1.2.8 zlib1g-dev: /usr/lib/x86_64-linux-gnu/libz.so ... $ cd /opt/microsemi/Libero_SoC_v11.9/Libero/lib $ mv libz.so.1 oldlibz.so.1 $ ln -s /lib/x86_64-linux-gnu/libz.so.1 libz.so.1

And then managed to launch it :

$ libero

But it’s unfortunately not finished.

First, when I tryied to synthesize I had this message in error window :

/opt/microsemi/Libero_SoC_v11.9/Synplify/bin/synplify_pro: 137: [: unexpected operator

/opt/microsemi/Libero_SoC_v11.9/Synplify/bin/synplify_pro: 151: [: !=: argument expected

/opt/microsemi/Libero_SoC_v11.9/Synplify/bin/synplify_pro: 324: /opt/microsemi/Libero_SoC_v11.9/Synplify/bin/config/execute: Syntax error: "(" unexpected (expecting ";;")

The problem come from the shell Debian uses by default :

$ ls -lha /bin/sh lrwxrwxrwx 1 root root 4 oct. 29 20:50 /bin/sh -> dash

This shell doesn’t work like bash and generate some error in synplify scripts. To solve it I simply changed the /bin/sh link to /bin/bash :

$ cd /bin/ $ sudo mv sh shold $ sudo ln -s bash sh

And I managed to synthesize my design.

…

But it’s not finished ! Once my bitstream generated I would like to download it on the IGLOO2 on kit. For that, we have to install correctly drivers for FlashPro5.

Directives are given in the official Microsemi Linux install guide, but udev syntax is false on Debian :

BUS=="usb",SYSFS{idProduct}=="2008",SYSFS{idVendor}=="1514",MODE="0660",GROUP="",SYMLINK+="FlashPro5"

BUS=="usb",SYSFS{idProduct}=="6001",SYSFS{idVendor}=="0403",MODE="0660",GROUP="",SYMLINK+="FTDI232"

Right rules are following :

# FlashPro5

SUBSYSTEM=="usb", ATTR{idVendor}=="1514", ATTR{idProduct}=="2008", MODE="0666", GROUP="plugdev"

SUBSYSTEM=="usb", ATTR{idVendor}=="0403", ATTR{idProduct}=="6001", MODE="0666", GROUP="plugdev"

Should be written in /etc/udev/rules.d/70-microsemi.rules file.

Then fully works and they lived happily and urged a lot of children

La référence en matière de livre sur l’architecture des processeurs. Tout y passe, l’arithmétique binaire, le langage assembleur, le datapath (le core d’un processeur), les pipelines et les différentes méthodes de prédiction de branches, les différentes architecture multicore, les GPU/VPU, la hiérarchie des mémoires, …

David A.Patterson est une superstar dans le milieu c’est lui qui est à l’origine de l’architecture de type «RISC». Et avec cette édition nous avons droit à une description fine du jeux d’instructions libre RISC-V très à la mode aujourd’hui. Tout en parlant principalement du RISC-V, le livre n’oublie pas les autres architectures célèbre comme x86, arm ou mips.

Le livre parait cher, mais vous en aurez pour votre argent tant le contenu est dense.