Par Bruno Levy, sur twitter :

Par Bruno Levy, sur twitter :

La présentation de Jonathan Bachrach donne les bases d’utilisation des interfaces Decoupled() en Chisel. Cependant, elle date (2013). Il est donc nécessaire de se mettre un peu à jour.

Tout d’abord, il ne faut pas oublier d’inclure le package :

import chisel3.util._Ensuite, l’interface possède en elle même l’information de direction. Il ne faut donc pas l’inclure dans un Output()/Input() lorsqu’on le déclare dans un IO(new Bundle {}) :

// Producteur

val data = Decoupled(UInt(10.W))

// Consommateur

val data = Flipped(Decoupled(UInt(10.W)))Et pour finir, on ne déclare plus de Reg() comme donné à la fin de la présentation. Il faut utiliser RegNext() à la place :

results.valid := isResult

results.bits := result

isResult := RegNext(results.ready) & haveNewResultTout cela évitera les horribles traces Java assez illisible.

Il y a plus de deux ans et demi maintenant, mzf publiait un journal sur le site LinuxFR parlant de son projet «TapTempo». L’objectif de son programme était simplement de mesurer la cadence d’une musique en tapant sur une touche de son clavier, le résultat s’affichant simplement dans la console.

Ce journal fut le point de départ d’une série de «projets TapTempo» proposé par les lecteurs du site dans à peu prêt tous les langages informatique possible… Mais pas le Verilog.

Voici donc la lacune comblée avec TapTempo en Verilog.

[Dépêche parue initialement sur LinuxFR]

Le projet TapTempo semble faiblir depuis quelques mois maintenant. En panne de langage informatique pour en faire une dépêche ?

Laissez‑moi vous présenter un langage assez particulier puisqu’il ne sert pas à faire de la programmation. Ce langage permet de décrire le comportement numérique d’un composant électronique (on parle alors de langage de description de matériel — HDL) : le Verilog.

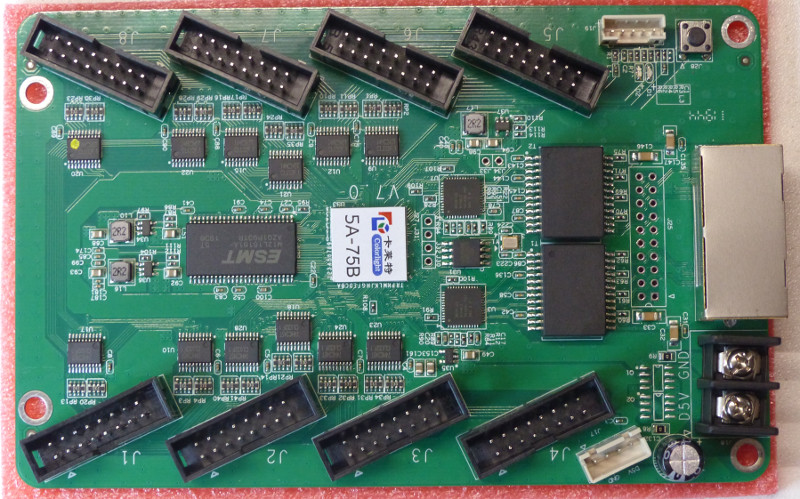

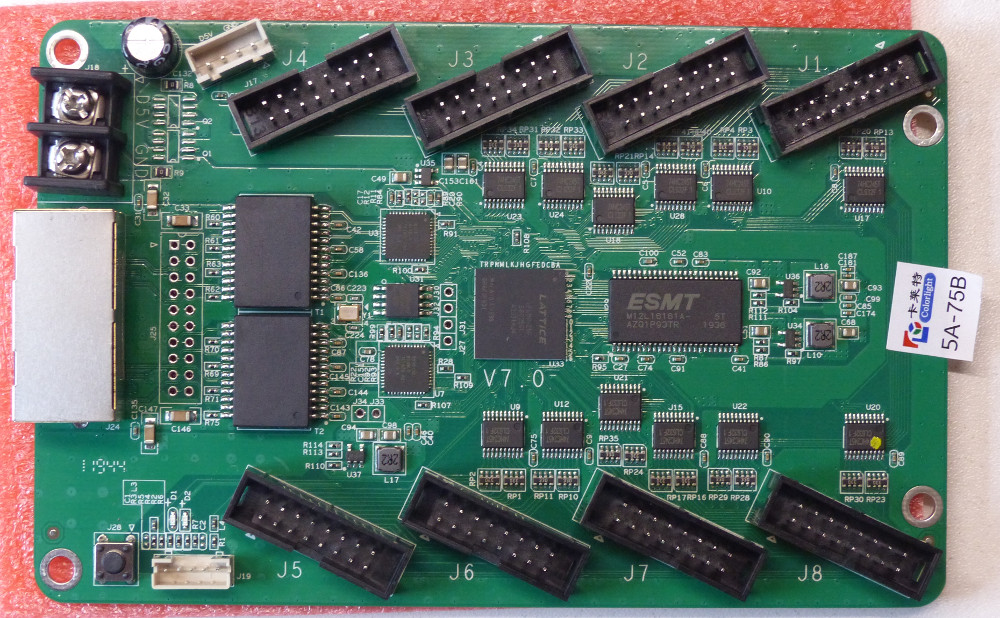

C’est aussi un langage utilisé pour faire de la synthèse numérique sur les circuits logiques programmables (FPGA). Dans cet exemple, nous utiliserons la carte de développement à bas coût ColorLight 5A‑75B.

Le Verilog est un langage conçu à l’origine pour rédiger des spécifications de circuits logiques en électronique numérique. Le langage permet de décrire le comportement de sortie par rapport à des entrées logiques.

Un peu comme les logiciels de saisie de schéma électronique, le Verilog est très hiérarchique, on décrit des modules avec leurs entrées-sorties. Que l’on assemble ensuite dans d’autres modules pour finir dans un module « top » qui décrit le composant final.

Dans le cas de TapTempo, le module « top » est déclaré comme ceci :

module taptempo #(

parameter CLK_PER_NS = 40, // 25Mhz clock (ns)

parameter TP_CYCLE = 5120, // timepulse cycle period (ns)

parameter BPM_MAX = 250 // BPM max (bpm)

)(

input clk_i,

input btn_i,

output pwm_o

);

//corps du module

endmoduleLe module possède deux entrées : l’horloge (clk_i) et le bouton (btn_i) ainsi qu’une sortie pwm (pwm_o) pour l’affichage. Les paramètres seront vus comme des constantes au moment de la simulation, ils permettent de configurer les composants en fonction de la cible.

Le changement de valeur des signaux se fait dans des processus qui sont déclenchés sur événement. Ces processus sont décrits au moyen du mot clef always@() en Verilog.

Par exemple, dans le code suivant:

/* Detect rising edge*/

reg btn_old, btn_rise;

always@(posedge clk_i)

begin

btn_old <= btn_i;

if(btn_old == 0 && btn_i == 1)

btn_rise <= 1;

else

btn_rise <= 0;

endL’événement déclencheur du process est le front montant de l’horloge clk_i. À chaque fois qu’un front montant d’horloge se présente, le processus est exécuté de manière séquentielle.

L’opérateur <= est l’opérateur d’affectation dit « non bloquant ». Cela signifie que la valeur ne sera effectivement appliquée qu’a la fin de l’exécution du process. Donc la valeur du signal btn_old ne sera pas nécessairement égale à btn_i à la ligne du if() comme on aurait pu instinctivement le croire.

Le langage Verilog a beaucoup de succès dans le monde du logiciel libre. En effet il est relativement peu verbeux et ressemble au C pour de nombreux aspects.

Il est par exemple possible de décrire des macros de la même manière qu’en C, il suffit de remplacer le symbole # par ` pour créer des constantes qui seront remplacées par le pré-processeur.

/* count tap period */

`define MIN_NS 60_000_000_000

`define BTN_PER_MAX (`MIN_NS/TP_CYCLE)

`define BTN_PER_SIZE ($clog2(1 + `BTN_PER_MAX))Le Verilog reprend également les opérateurs booléen et binaire &,&&, |,||, etc. du C.

C’est le langage HDL le mieux supporté par les différents logiciels libres. Si l’on souhaite se lancer dans le domaine des FPGA et/ou des ASIC, il est préférable de commencer par lui. C’est également le langage « de sortie » de quasiment tous les générateurs de code HDL.

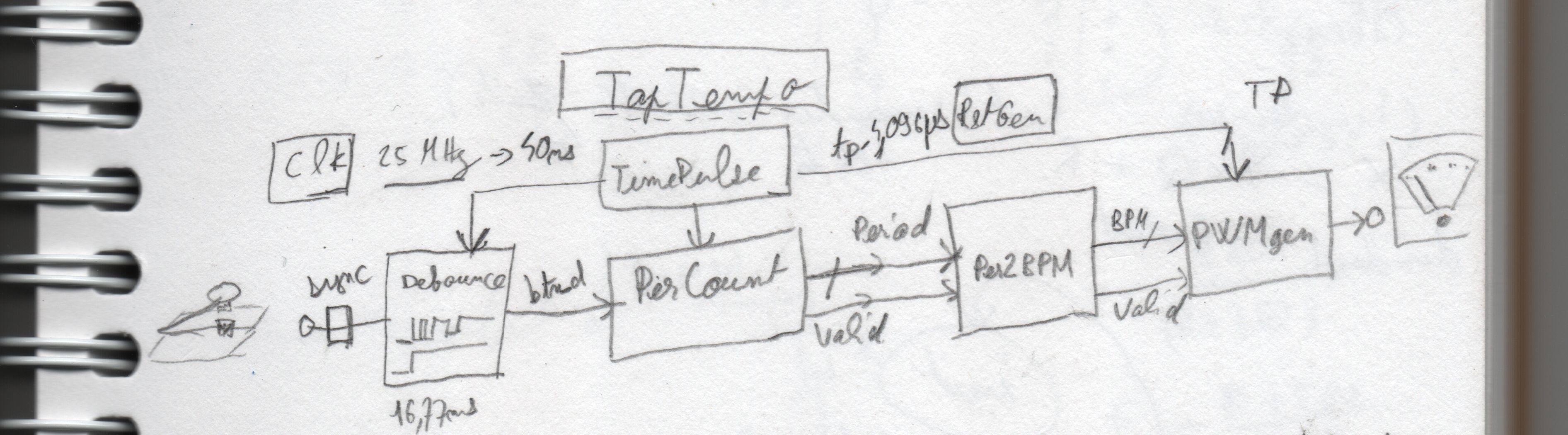

L’outil indispensable pour commencer un projet en Verilog est… le papier et le crayon. Il est en effet indispensable d’avoir une vue d’ensemble assez claire de ce que l’on souhaite réaliser avant de se lancer dans le code.

Voici donc l’architecture générale du composant TapTempo :

Même si l’on doit revenir plusieurs fois (ce qui est le cas ici puisque les constantes ne sont pas à jour) sur ce schéma général en cours de développement, cette partie est très importante. Si elle est bien pensée, le reste coule de source.

Le composant va nécessiter quelques compteurs, mais l’horloge utilisée ici étant très rapide nous allons d’abord factoriser le comptage au moyen du module nommé timepulse, ce module va distribuer un pulse qui servira de base aux autres compteurs pour leur fonctionnement interne.

L’entrée utilisateur se compose d’un bouton (touche télégraphique « morse »). Les fronts montant et descendant de cette entrée n’étant pas synchronisés sur l’horloge du système nous allons devoir le faire au moyen de deux bascules en série pour éviter la métastabilité.

/* Synchronize btn_i to avoid metastability*/

reg btn_old, btn_s;

always@(posedge clk_i or posedge rst)

begin

if(rst) begin

btn_old <= 1'b0;

btn_s <= 1'b0;

end else begin

btn_old <= btn_i;

btn_s <= btn_old;

end

endLe second problème que pose notre entrée est que l’appui sur le bouton ne génère pas des changements francs de son état. Chaque « appui et relâche » génère une série de rebonds et donc une série de 0 et de 1 avant de se stabiliser. Pour lisser le signal il va donc falloir faire passer le signal dans le bloc « anti-rebond » debounce.

Le bloc percount va ensuite se charger de mesurer le temps entre deux appuis sur le bouton. Cette période va devoir être transformée en fréquence « BPM » (Beat Per Minute) via le module per2bpm puis en une valeur pseudo-analogique (PWM) grâce au module pwmgen.

La carte cible ne possédant pas de bouton « reset », il va falloir le générer grâce au module rstgen de manière à s’assurer de l’état de départ de notre système au démarrage.

La plupart des programmes TapTempo proposés jusqu’ici supposaient – en plus d’un CPU – la présence d’un clavier et d’une console texte de sortie (avec toute la pile de pilotes et de système d’exploitation associés). Ici, nous allons devoir tout définir dans le « portegramme » – Dans l’industrie on va parler d’IP pour Intellectual Property, quel horrible nom –.

L’idée est donc de simplifier au maximum l’entrée « clavier » et la sortie histoire de pouvoir les décrire simplement.

Pour l’entrée nous allons nous contenter d’un contact de type bouton, ou d’une touche de type télégraphe « morse ».

Comme on peut le voir dans le schéma ci-dessus, quand la touche est appuyée, l’entrée « bouton » est mise à la masse et donne un niveau logique à 0 sur notre système. Lorsque l’on relâche le bouton, la résistance de tirage ramène le niveau de tension à Vcc pour avoir un niveau 1 sur l’entrée.

Pour la sortie, l’idée de mettre un écran complexifie énormément le système. En effet, il est nécessaire de faire une machine d’état assez complexe pour initialiser l’écran puis rafraîchir l’affichage. Il est souvent nécessaire d’ajouter un processeur « soft » rien que pour ça d’ailleurs. (Bon il est vrai que le VGA n’est pas si compliqué, mais il reste plus complexe que la solution proposée ici).

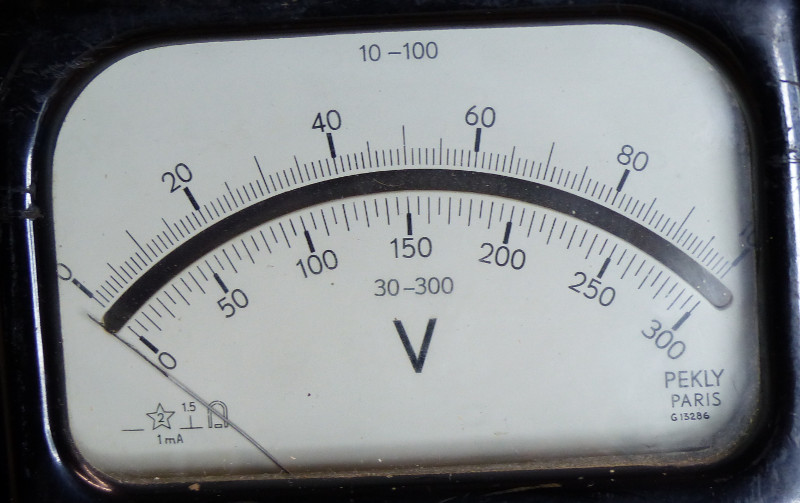

Non, l’idée ici est d’utiliser les graduations de l’antique voltmètre à aiguille trouvé dans une cave et qui gradue de 0 à 300 comme on peut le voir sur la photo :

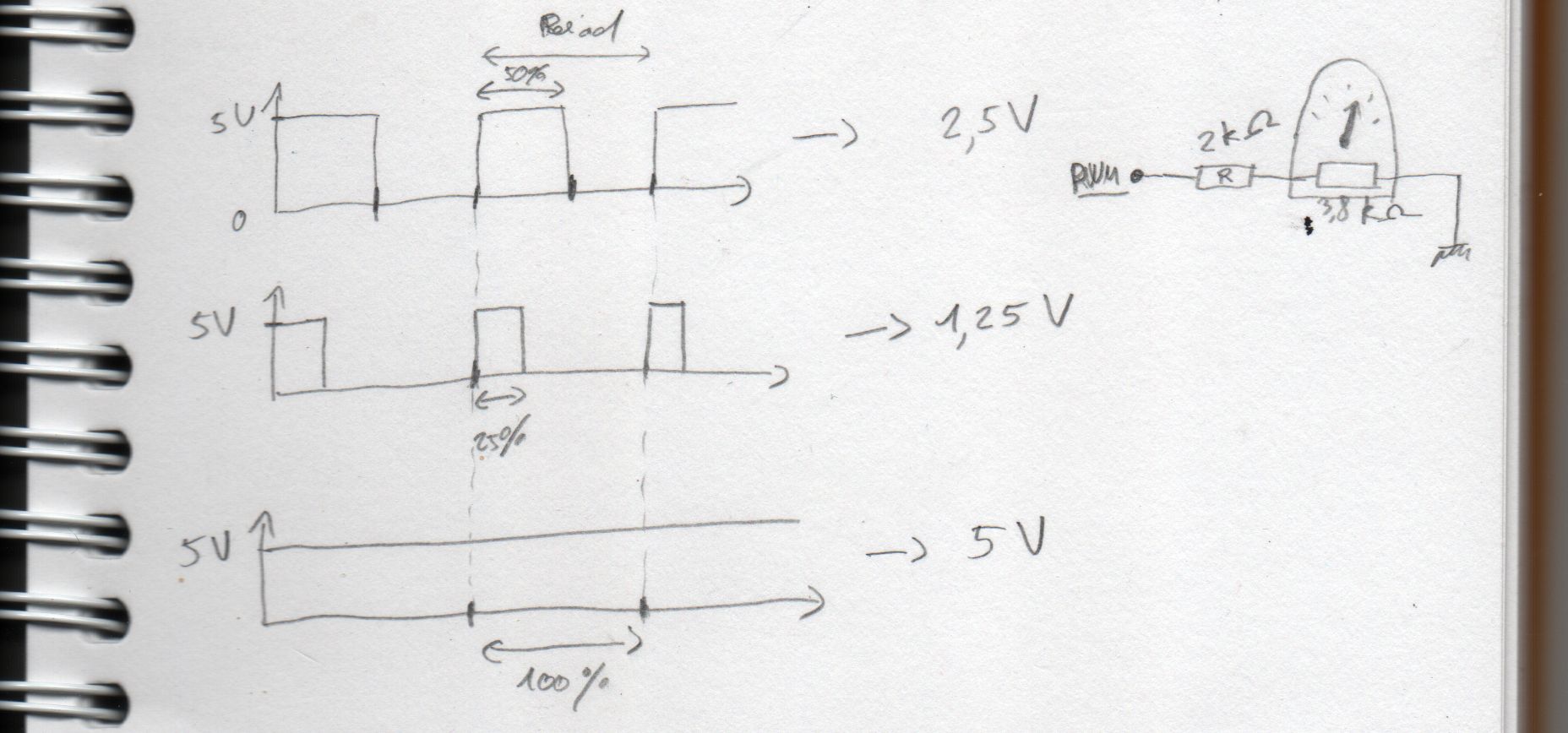

Et comme un système numérique ne sort que des 0 et des 1 sur ses broches, on va « simuler » une valeur analogique au moyen d’une PWM (Pulse With Modulation). Il suffit de changer le rapport cyclique entre le temps haut et le temps bas de notre signal pour faire varier la tension moyenne qui sera vue par le voltmètre. Si on l’ajuste correctement avec une résistance en série, il est relativement facile de forcer la valeur maximale (5V) à 250.

La période de la pwm sera configurée suffisamment rapide pour que l’aiguille n’oscille pas.

Le module ne prend pas de valeur d’entrée hormis l’horloge et le reset qui sont de rigueur dans tout le projet. Son signal de sortie tp_o est une pulsation de l’horloge émise toutes les 5120 ns :

module timepulse #(

parameter CLK_PER_NS = 40,

parameter PULSE_PER_NS = 5120

)(

/* clock and reset */

input clk_i,

input rst_i,

/* output */

output tp_o);Pour pouvoir compter des périodes de 5120ns on définit un registre de comptage :

`define MAX_COUNT (PULSE_PER_NS/CLK_PER_NS)

`define MAX_COUNT_SIZE ($clog2(`MAX_COUNT))

reg [`MAX_COUNT_SIZE-1:0] counter = 0;Puis on compte de manière synchronisée avec l’horloge :

always@(posedge clk_i or posedge rst_i)

begin

if(rst_i)

begin

counter <= 0;

end else begin

if (counter < `MAX_COUNT)

begin

counter <= counter + 1'b1;

end else begin

counter <= 0;

end

end

endLa pulsation est émise lorsque le compteur passe par 0 :

assign tp_o = (counter == 0);L’entrée de ce module est le signal de bouton préalablement synchronisé avec l’horloge du système btn_s. Le compteur utilisera la pulsation tp_i généré par le module timepulse décrit ci-avant.

La sortie du module est un signal btn_o proprement lissé. La période de temporisation de 20 ms est donné ici en paramètre DEBOUNCE_PER_NS.

module debounce #(

parameter PULSE_PER_NS = 5120,

parameter DEBOUNCE_PER_NS = 20_971_520

)(

/* clock and reset */

input clk_i,

input rst_i,

/* inputs */

input tp_i,

input btn_i,

/* output */

output btn_o

);La gestion des rebonds est réalisée au moyen d’un compteur utilisé pour temporiser.

`define MAX_COUNT ((DEBOUNCE_PER_NS/PULSE_PER_NS)-1'b1)

`define MAX_COUNT_SIZE ($clog2(`MAX_COUNT))

/* Counter */

reg [`MAX_COUNT_SIZE-1:0] counter = 0;Ainsi que d’une machine d’états à 4 états :

/* State machine */

localparam [1:0] s_wait_low = 2'h0,

s_wait_high = 2'h1,

s_cnt_high = 2'h2,

s_cnt_low = 2'h3;

reg [1:0] state_reg, state_next;Les transitions de la machine d’états sont données dans le code ci-dessous dans un processus dit « combinatoire » (always@*) par opposition à un processus « synchrone ».

always@*

begin

case(state_reg)

s_wait_low:

if(btn_i)

state_next = s_cnt_high;

else

state_next = s_wait_low;

s_wait_high:

if(!btn_i)

state_next = s_cnt_low;

else

state_next = s_wait_high;

s_cnt_high:

/* verilator lint_off WIDTH */

if(counter == `MAX_COUNT)

/* verilator lint_on WIDTH */

state_next = s_wait_high;

else

state_next = s_cnt_high;

s_cnt_low:

/* verilator lint_off WIDTH */

if(counter == `MAX_COUNT)

/* verilator lint_on WIDTH */

state_next = s_wait_low;

else

state_next = s_cnt_low;

endcase;

endL’état de la machine est tout de même synchronisé dans un second processus :

always@(posedge clk_i or posedge rst_i)

if(rst_i)

state_reg <= s_wait_low;

else

state_reg <= state_next;Le principe de « lissage » des rebonds est donc le suivant : Dans l’état initial s_wait_low on attend que le bouton passe à la valeur 1. Lorsque le signal passe à 1, on change d’état pour s_cnt_high.

Le passage dans l’état s_cnt_high a pour effet de faire passer le signal de sortie à 1 et déclencher le compteur. Tant que le compteur compte et n’a pas atteint la valeur MAX_COUNT, on reste dans cet état quelles que soient les variations du signal d’entrée.

Lorsque le compteur atteint la valeur maximale, la machine d’état passe dans l’état s_wait_high (en attente de valeurs hautes).

Dans l’état s_wait_high on surveille la valeur du bouton d’entrée, si elle passe à 0 on change d’état pour s_cnt_low.

De manière symétrique à s_cnt_high on déclenche donc le compteur en ignorant la valeur d’entrée. Et, lorsqu’elle atteint son maximum on passe à l’état initial s_wait_low.

La valeur « lissée » du bouton en sortie est donnée par l’état de la machine d’état :

assign btn_o = (state_reg == s_cnt_high) || (state_reg == s_wait_high);L’interface du module percount se compose des entrées habituelles d’horloge clk_i, de reset rst_i ainsi que de la pulsation tp_i.

Le signal de mesure en entrée est btn_i et la sortie est un vecteur btn_per_o donnant la valeur mesurée. La valeur est considérée comme valide uniquement lorsque la sortie btn_per_valid est à 1. Cette astuce permet d’économiser un registre si la sauvegarde de la valeur mesurée est inutile comme c’est le cas ici.

`define MIN_NS 60_000_000_000

`define BTN_PER_MAX (`MIN_NS/TP_CYCLE)

`define BTN_PER_SIZE ($clog2(1 + `BTN_PER_MAX))

module percount #(

parameter CLK_PER_NS = 40,

parameter TP_CYCLE = 5120,

parameter PULSE_PER_NS = 5120,

)(

/* clock and reset */

input clk_i,

input rst_i,

/* time pulse */

input tp_i,

/* input button */

input btn_i,

/* output period */

output [(`BTN_PER_SIZE-1):0] btn_per_o,

output btn_per_valid);Maintenant que nous avons un signal de bouton btn_b propre et lissé, nous pouvons entamer la mesure de la période entre deux appuis au moyen de… devinez quoi ? D’un compteur pardi !

reg [($clog2(`BTN_PER_MAX+1)-1):0] counter = 0;

reg counter_valid = 0;

assign btn_per_valid = counter_valid;

assign btn_per_o = counter;Il nous faut tout d’abord détecter le front descendant du bouton :

reg btn_old;

wire btn_fall = btn_old & (!btn_i);

always@(posedge clk_i or posedge rst_i)

begin

if(rst_i)

btn_old <= 1'b0;

else

btn_old <= btn_i;

endLe signal btn_fall sert de remise à zéro du compteur ainsi que de validation de la valeur de sortie :

always@(posedge clk_i or posedge rst_i)

begin

if(rst_i)

begin

counter <= 0;

end else begin

if(btn_fall) begin

counter_valid <= 1'b1;

end else if(counter_valid) begin

counter <= 0;

counter_valid <= 1'b0;

end else begin

/* stop counting if max, count tp_i */

if(tp_i && counter < `BTN_PER_MAX)

counter <= counter + 1'b1;

end

end

endLe compteur compte le nombre de pulsations de tp_i jusqu’à atteindre la saturation BTN_PER_MAX. Si un front montant du bouton se présente avec btn_fall, on valide le compteur avec counter_valid. Et si le signal de validation passe à 1 (donc le coup d’horloge suivant) on remet le compteur à zéro et on recommence à compter.

Avec le module per2bpm on arrive dans la partie critique du projet, car il va nous falloir faire une division. On entre une période dans le module :

/* inputs */

input [(`BTN_PER_SIZE-1):0] btn_per_i,

input btn_per_valid,Et on doit en ressortir une fréquence (BPM) :

/* outputs */

output [`BPM_SIZE - 1:0] bpm_o,

output bpm_validSuivant la formule :

Il faut donc diviser la constante

par la variable

La division (tout comme la multiplication) est un point sensible en Verilog. En effet, l’opérateur de division existe bien dans le langage et il se peut que cela simule parfaitement.

C’est lorsque arrivera l’étape de la synthèse que l’on risque d’avoir quelques surprises. Il est possible que certains logiciels de synthèse réussiront à faire quelque chose en un coup d’horloge. Mais il est certain que cela se fera au prix de très mauvaises performances en matière de ressources utilisées et de fréquence d’horloge. Il est surtout probable que votre logiciel de synthèse jette l’éponge.

Pour réaliser cette division, nous allons donc en revenir aux fondamentaux appris au primaire et poser la division. Une division, c’est la recherche du Quotient et du Reste de l’équation suivante :

reg [(`REGWIDTH-1):0] divisor;

reg [(`REGWIDTH-1):0] remainder;

reg [(`REGWIDTH-1):0] quotient;La taille des registres sera celle de la période en entrée BTN_PER_SIZE additionné à la constante à diviser.

`define DIVIDENTWITH ($clog2(1 + `MIN_NS/(TP_CYCLE)))

`define REGWIDTH (`BTN_PER_SIZE + `DIVIDENTWITH)La division s’effectue avec une série de soustraction du reste (remainder) et de décalage du diviseur.

À l’étape initiale, on place le diviseur à gauche du registre divisor et le dividende dans le reste remainder :

divisor <= {btn_per_i, (`DIVIDENTWITH)'h0};

remainder <= `MIN_NS/TP_CYCLE;

// le résultat est initialisé à 0:

quotient <= 0;Puis on effectue une série de comparaison-soustraction-décalage avec l’algorithme comme décrit ci-dessous :

divisor) inférieur ou égal au reste (remainder), on soustrait le reste avec le diviseur et on décale le quotient à gauche en ajoutant 1 : if(divisor <= remainder)

begin

remainder <= remainder - divisor;

quotient <= {quotient[(`DIVIDENTWITH-2):0], 1'b1};divisor) est supérieur au reste, on décale le quotient à gauche en ajoutant 0. On ne touche pas au reste : quotient <= {quotient[(`DIVIDENTWITH-2):0], 1'b0}; divisor <= {1'b0, divisor[(`REGWIDTH-1):1]};La division est orchestrée par une machine à trois états :

localparam [1:0] s_init = 2'h0,

s_compute = 2'h1,

s_result = 2'h2;

reg [1:0] state_reg, state_next;Et le résultat est disponible en sortie quand state_reg est dans l’état s_result:

assign bpm_o = quotient[(`BPM_SIZE-1):0];

assign bpm_valid = (state_reg == s_result);La génération du signal pseudo analogique décrite en introduction est presque la partie la plus simple.

On compte (oui encore) de 0 à 250 (BPM_MAX) :

/* count */

always@(posedge clk_i or posedge rst_i)

begin

if(rst_i)

count <= BPM_MAX;

else begin

if(tp_i)

begin

if (count == 0)

count <= BPM_MAX;

else

count <= count - 1'b1;

end

end

endEt on passe le signal de sortie pwm_o à 1 lorsque le compteur est inférieur à la fréquence demandée :

assign pwm_o = (count <= pwmthreshold);Il y a juste une subtilité consistant à sauvegarder la valeur de la fréquence donnée en entrée dans deux registres pwmthreshold et bpm_reg :

reg [($clog2(BPM_MAX+1)-1):0] bpm_reg;

reg [($clog2(BPM_MAX+1)-1):0] pwmthreshold;

/* Latching bpm_i on bpm_valid */

always@(posedge clk_i or posedge rst_i)

begin

if(rst_i)

begin

bpm_reg <= 0;

pwmthreshold <= 0;

end else begin

if(bpm_valid)

bpm_reg <= bpm_i;

if(count == BPM_MAX)

pwmthreshold <= bpm_reg;

end

endLe premier registre bpm_reg est mis à jour lorsque le signal d’entrée bpm_valid est à 1. Pour mémoriser la valeur d’entrée et pouvoir l’utiliser au moment où l’on en a besoin.

Et le second pwmthreshold est rafraîchi en fin de cycle d’une période de la pwm. Pour éviter d’avoir un changement de valeur en cours de période, et donc un rapport cyclique faux.

Jusqu’ici nous avons décrit le comportement du composant final en Verilog. Toutes les développeuses ou développeurs HDL le savent très bien, il est impossible de réaliser un projet Verilog (ou autre HDL) sans faire un minimum de simulation.

Pour simuler le composant, il est nécessaire de décrire les stimuli en entrée du composant et de lire/valider les sorties. On va généralement créer un composant hiérarchiquement au-dessus du top de notre composant appelé « testbench » dans lequel nous décrirons les changements de valeurs des entrées au cours du temps. Cette partie peut tout à fait se faire en Verilog.

Cependant, l’idée de mélanger la partie banc de test et composant « synthétisable » n’est pas terrible. En effet on va très vite confondre les deux parties et mélanger les codes. L’exemple de la division est criant : l’opérateur diviser « / » fonctionne très bien dans la partie testbench mais elle pose de gros problèmes dans la partie « synthétisable ».

Pour éviter ce mélange des genres, une solution radicale consiste à utiliser un autre langage pour la partie banc de test. Le C++ et le SystemC sont utilisés depuis longtemps pour cela. S’ils sont utilisés en conjonction avec Verilator ils permettent d’atteindre des puissance/rapidité de simulation inégalées par les simulateurs « propriétaires ».

Une autre méthode consiste à piloter le simulateur Verilog avec un autre programme, on parle alors de cosimulation. C’est le cœur du fonctionnement du module python CocoTB. L’idée ici est d’écrire son banc de test en python, ce qui est nettement plus confortable que du Verilog ou même du C++ (SystemC est une librairie C++ également).

Le testbench pour simuler l’ensemble du projet taptempo se trouve dans le répertoire cocotb/test_taptempo. Pour le simuler il suffit de s’y rendre et d’y exécuter un make.

À condition cependant d’avoir installé cocotb (en python3) et Icarus pour la partie simulateur (On laissera l’appréciation de l’installation au lecteur en fonction de ses affinités linuxdistributive).

La simulation consiste à tester trois appuis sur le bouton à des intervalles différents :

@cocotb.test()

async def debounce_upanddown(dut):

td = TestTapTempo(dut)

td.log.info("Running test!")

await td.reset()

td.log.info("System reseted!")

await Timer(1000, units="us")

td.log.info("up")

await td.bounce_up(10, bounce_per=(10000, "ns"))

await Timer(24, units="ms")

td.log.info("down")

await td.bounce_down(10, bounce_per=(10000, "ns"))

await Timer(300, units="ms")

td.log.info("up")

await td.bounce_up(10, bounce_per=(10000, "ns"))

await Timer(30, units="ms")

td.log.info("down")

await td.bounce_down(10, bounce_per=(10000, "ns"))

await Timer(800, units="ms")

td.log.info("up")

await td.bounce_up(10, bounce_per=(10000, "ns"))

await Timer(30, units="ms")

td.log.info("Wait stable")

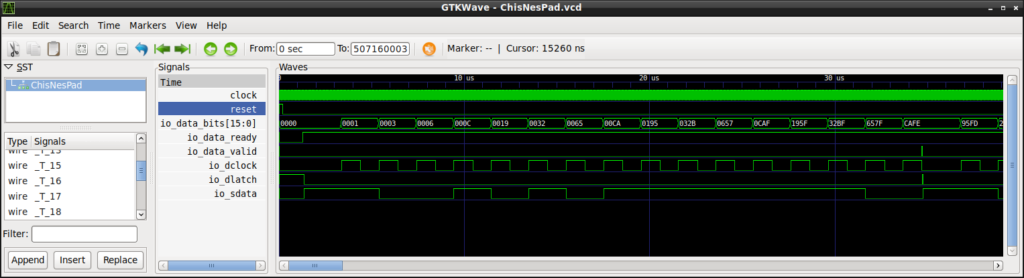

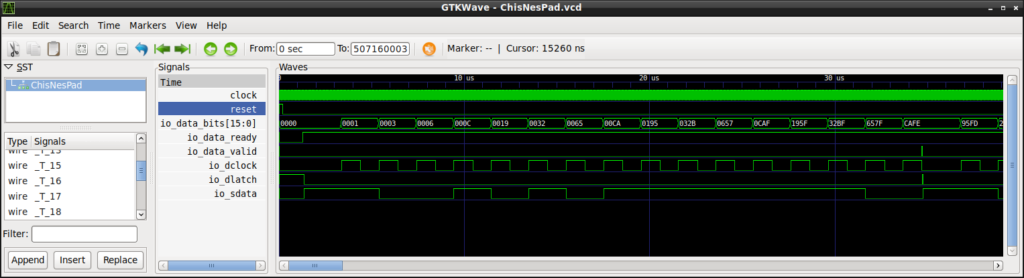

await Timer(1000, units="us")Cela génère un fichier de « traces » au format VCD particulièrement volumineux de 2,3 Go (qui se compresse à 70 Mo avec xz !) permettant de visionner les signaux au cours du temps grâce à gtkwave:

$ gtkwave -g taptempo.vcdEt donne la trace suivante :

Cette simulation est particulièrement longue (il m’a fallu environ une heure et demie sur mon vieux T430) et génère un fichier de trace monstrueux. En phase de développement on va généralement lancer de petites simulations par modules comme on peut le voir pour le module debounce dans le répertoire cocotb/test_debounce. On changera également certaines constantes de temps pour limiter les « pas » de simulation consommant inutilement du calcul processeur.

Il est également possible de laisser l’ordinateur écrire les stimuli grâce à la méthode de preuve formelle. C’est la méthode qui a été utilisée ici pour les modules. Les fichiers de configuration se trouvent dans le répertoire formal/*.

La Colorlight n’est pas initialement une carte de développement pour les FPGA. C’est une carte permettant de piloter des panneaux de LED qui nous agressent un peu partout dans les rues commerçantes. Cependant, un petit malin s’est rendu compte qu’elle était munie d’un FPGA de chez Lattice : l’ECP5.

Ce FPGA possède deux gros avantages :

Jusqu’à la colorlight, les kits de développement ECP5 n’étaient pas donnés puisque les premières cartes débutaient à 100 $ minimum. Mais avec la colorlight, on tombe à 15 $, ce qui en fait un kit de développement ultra bon marché pour se faire la main avec des FPGA.

Et comme tout est opensource, il est aisé d’aller installer les logiciels permettant de synthétiser TapTempo sur sa distribution Linux préférée.

L’explication de l’installation des outils est hors de propos de cet article (un article détaillé sur la colorlight est disponible dans le Hackable 35), mais une fois les outils installés, il suffit de se rendre dans le répertoire synthesis/colorlight du projet et de faire make :

$ make

[...]

Info: Device utilisation:

Info: TRELLIS_SLICE: 328/12144 2%

Info: TRELLIS_IO: 3/ 197 1%

Info: DCCA: 1/ 56 1%

Info: DP16KD: 0/ 56 0%

Info: MULT18X18D: 0/ 28 0%

Info: ALU54B: 0/ 14 0%

Info: EHXPLLL: 0/ 2 0%

Info: EXTREFB: 0/ 1 0%

Info: DCUA: 0/ 1 0%

Info: PCSCLKDIV: 0/ 2 0%

Info: IOLOGIC: 0/ 128 0%

Info: SIOLOGIC: 0/ 69 0%

Info: GSR: 0/ 1 0%

Info: JTAGG: 0/ 1 0%

Info: OSCG: 0/ 1 0%

Info: SEDGA: 0/ 1 0%

Info: DTR: 0/ 1 0%

Info: USRMCLK: 0/ 1 0%

Info: CLKDIVF: 0/ 4 0%

Info: ECLKSYNCB: 0/ 10 0%

Info: DLLDELD: 0/ 8 0%

Info: DDRDLL: 0/ 4 0%

Info: DQSBUFM: 0/ 8 0%

Info: TRELLIS_ECLKBUF: 0/ 8 0%

Info: ECLKBRIDGECS: 0/ 2 0%

[...]

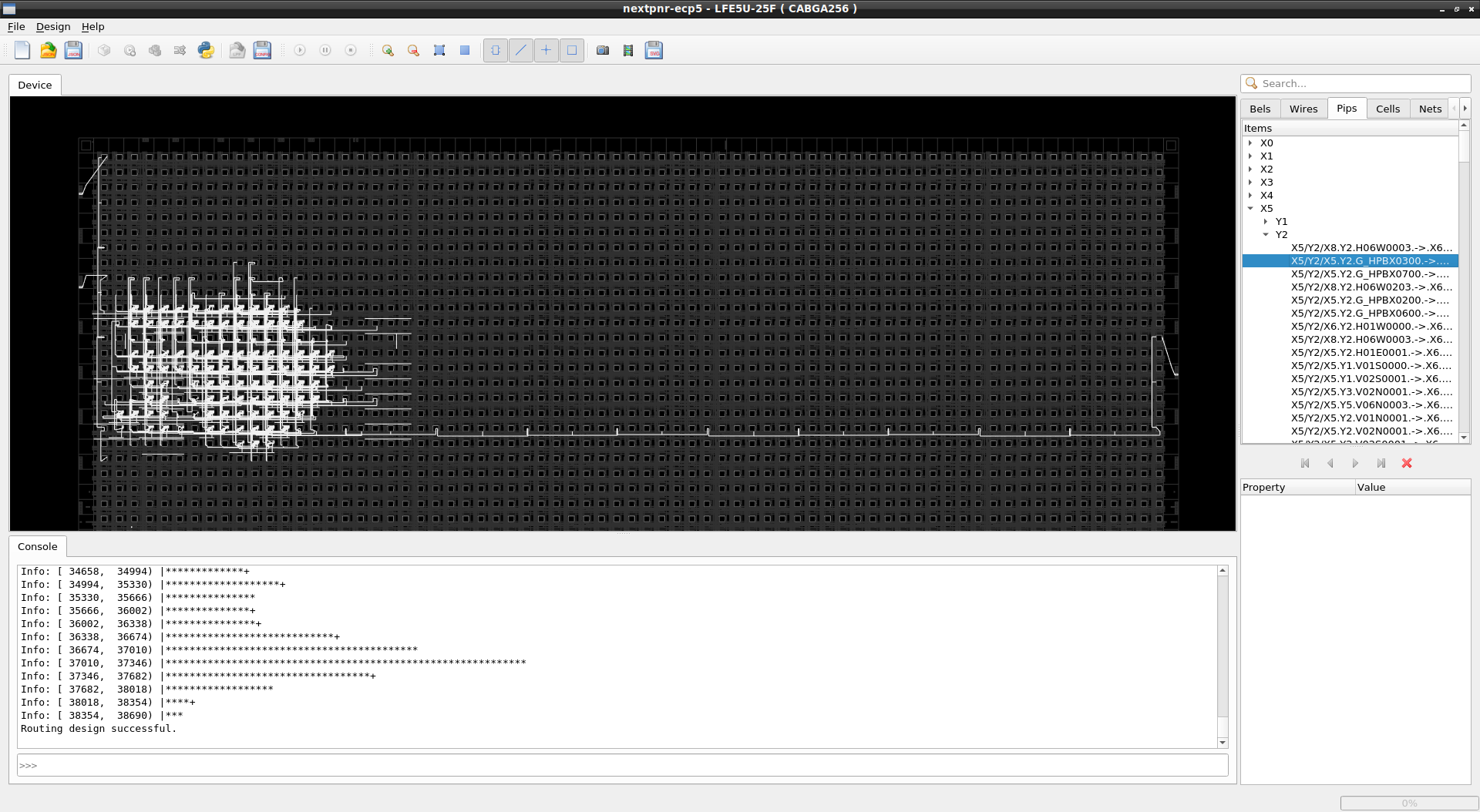

ecppack --svf taptempo.svf taptempo_out.config taptempo.bitOn voit ici que les ressources utilisées pour TapTempo sont ridicules par rapport au FPGA utilisé. La curieuse ou le curieux qui voudra « voir » le placement routage dans le FPGA utilisera l’option --gui dans la commande NextPnR pour avoir l’interface graphique :

$ nextpnr-ecp5 --25k --package CABGA256 --speed 6 --json taptempo.json --textcfg taptempo_out.config --lpf taptempo.lpf --freq 25 --guiCe qui donne un autre aperçu du remplissage du FPGA.

Pour télécharger le bitstream dans le FPGA, on pourra utiliser openFPGALoader en donnant simplement le nom du bitstream :

$ openFPGALoader taptempo.bitPour celles et ceux qui ont suivi jusqu’ici et qui voudraient se faire la main avec ce projet, voici quelques propositions de « sujet de TP » :) :

N’hésitez pas à me proposer des demandes d’intégration Git pour améliorer le projet.

On voit que dès que l’on passe dans le domaine de l’embarqué les choses se compliquent et prennent plus de temps. Alors que sur un PC on aurait pu faire ça en une ligne de code, quand on embarque ça dans un microcontrôleur, c’est déjà plus compliqué. Mais si l’on passe dans le monde des FPGA et des ASIC, le projet prend une toute autre dimension. C’est la raison pour laquelle il faut toujours se demander si un FPGA est bien à propos pour notre projet, non seulement cela coûtera plus cher en composant qu’une solution sur étagère, mais en plus le temps de développement (et donc le coût) sera nettement supérieur.

L’idée d’utiliser une touche de télégraphe pour mesurer le tempo n’était peut‑être pas la meilleure, compte tenu des rebonds qui sont relativement violents. Même avec le module lisseur de rebond (debounce), il subsiste quelques rebonds trop longs. Un tempo maximum à 250 n’est pas si rapide et l’on est vite frustré de l’atteindre alors qu’on pourrait mesurer des tempos de musiques plus… rythmées. On peut facilement passer à 300, mais ça reste lent. Si l’on veut un tempo plus rapide, il faut tout d’abord changer la graduation sur le voltmètre, puis modifier le paramètre BPM_MAX dans le code.

On a ici un modèle de projet qui est facile à synthétiser sur n’importe quel petit FPGA. C’est un projet qui peut être intéressant si l’on souhaite se sortir un peu les doigts des LED qui clignotent. La démonstration étant faite du fonctionnement de l’architecture globale, il est aisé de s’en servir pour la réécrire dans d’autres langages de description de matériel comme le VHDL, Chisel (même s’il y en a déjà une pour taptempo), Migen/Litex, MyHDL, Clash (en plus, ça permettrait de débloquer la dépêche LinuxFr.org sur le sujet)…

Pour le curieux, ou la curieuse, qui sera allé voir le code sur le projet GitHub, ce projet a été développé avec une dose de preuves formelles grâce au logiciel libre Yosys-SMTBMC.

[Dépêche publiée initialement sur LinuxFR]

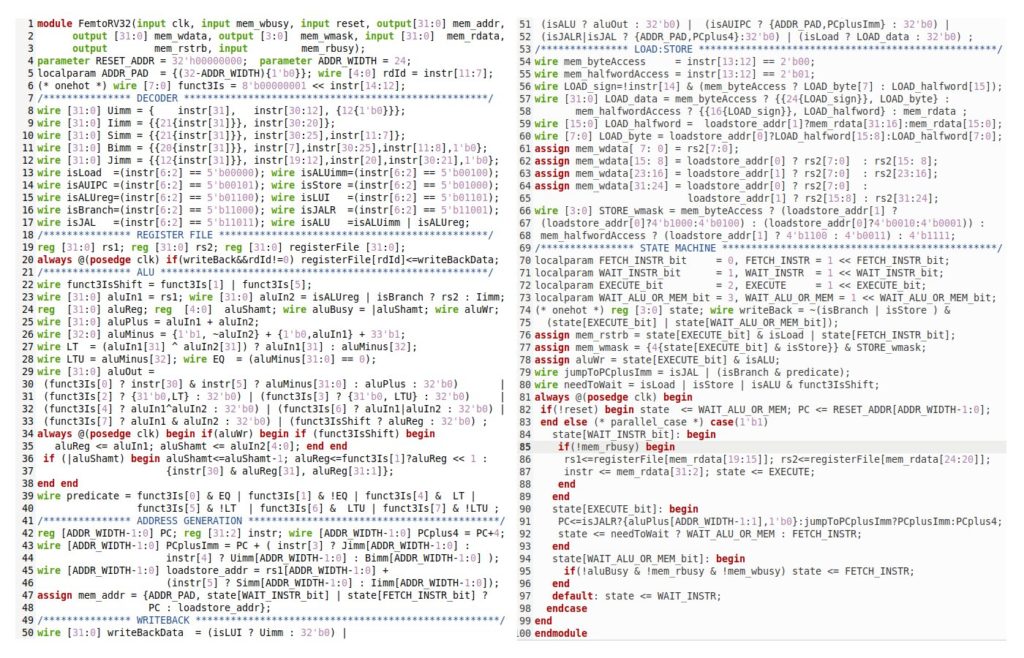

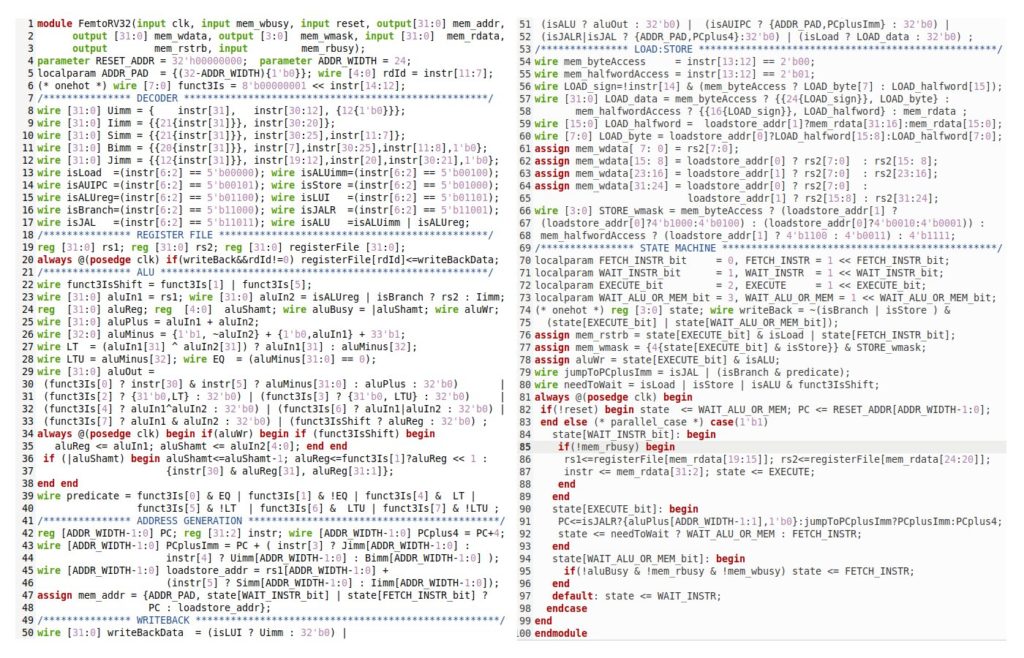

La libération des FPGA s’accélère à grands pas, il devient presque difficile de suivre toutes les nouvelles sur le sujet. Mais les FPGA ne doivent pas nous faire oublier leurs grands frères que sont les ASIC.

Un FPGA est un composant ayant un silicium déjà « gravé » mais où il est possible de reconfigurer les connexions entre les éléments logiques à volonté. Dans le cas d’un ASIC, on va cette fois graver directement les transistors sur un silicium vierge et les relier via des couches métaliques une fois pour toutes. Il ne faut surtout pas se planter à l’étape de conception car on ne pourra pas modifier les interconnexions une fois la production lancée.

Pour réaliser un ASIC, il faut fournir un plan des masques de chaque couche de dopage du silicium ainsi que des couches métaliques. Voici par exemple la représentation d’une bascule D :

Pour ce faire, on va partir d’une description RTL (Register Transfert Level) du composant, similaire aux descriptions utilisées pour les FPGA – la plupart du temps du Verilog ou du VHDL — que nous allons « synthétiser » en une Netlist. La suite va ressembler (de loin) à du placement‐routage et de la simulation analogique‐numérique, comme on peut le voir avec la conception de carte électronique.

Le flot de conception typique du monde du matériel est donné dans une des diapositives de la présentation de Tim Ansell ci‑dessous :

La partie langage de description du matériel et simulation est déjà largement libérée. Il existe des tas de composants open source décrits en VHDL et/ou en Verilog à présent. Les outils de synthèse libres arrivent aujourd’hui à maturité avec Yosys, bien sûr, pour le Verilog (et bientôt mature pour le VHDL grâce au greffon GHDL-yosys), mais aussi Alliance pour le VHDL.

Les trois piliers logiciels (EDA pour les outils, PDK les données et RTL le design) permettant de réaliser un ASIC sont donnés dans une autre diapo de Tim ci‑dessous :

Une fois la description « RTL » du composant synthétisée, il nous reste beaucoup d’étapes à franchir avant d’obtenir une description des masques de gravure permettant la fabrication proprement dite. Toutes ces étapes nécessitent l’utilisation de logiciels spécifiques pour réaliser les masques, construire l’arbre d’horloge, simuler en analogique certaines parties, concevoir les alimentations… Beaucoup de logiciels libres existent pour cela, tous ne sont pas matures ou restent très universitaire dans leur version open source. Mais il est possible de les utiliser tout de même pour réaliser un composant, comme l’a démontré Tim Edwards avec le Raven (un microcontrôleur RISC‑V à base de PicoRV32).

Cependant, même s’il n’a utilisé que des logiciels libres pour réaliser le Raven, Tim n’a pas pu accéder à la description physique des composants numériques qu’il utilisait. Il a dû se contenter de « boîtes noires » représentant chaque fonction logique à assembler pour réaliser le microcontrôleur. En effet, tous ces logiciels libres demeurent quasiment inutiles si l’on n’a pas accès à la description physique de la technologie cible utilisée. Les fondeurs de silicium fournissent un PDK (process design kit) contenant des bibliothèques de composants avec la description physique de leurs technologies, ainsi que la géométrie de chaque transistor et les modèles de simulations spice permettant de valider le comportement analogique. Et pour avoir accès à ces PDK, la vente de vos deux reins ne suffira pas, même si vous signez les triples NDA (accord de non‑divulgation) avec votre sang. Ce PDK reste le gros frein à la libération du matériel, un caillou dans la chaussure du matériel libre. C’est ce que Google a bien compris en finançant le développement d’un PDK libre via la société SkyWater : le SKY130.

La publication du SKY130 vient d’être annoncée cette semaine par Tim Ansell lors d’un « dial‑up » de la FOSSi Foundation. Comme son nom l’indique, ce PDK cible la technologie 130 nm. Cette taille de gravure peut sembler obsolète quand on sait qu’Intel fabrique de plus en plus en 7 nm, et commence même à tester le 4 nm. Mais les chaînes de fabrication de silicium avec cette finesse de gravure permettent un coût de production très raisonnable pour des performances qui ne sont pas non plus ridicules. SiFive, par exemple, a sorti un microcontrôleur 32 bits RISC‑V (E310) gravé en 180 nm et tout de même cadencé à 320 MHz. Il est donc possible de réaliser beaucoup de chose avec du 130 nm.

Et pour promouvoir son PDK et fédérer une communauté de passionnés, hobbyistes, universitaires, « startupeuses », etc., Google a décidé de produire quarante projets à base de ce PDK tous les six mois et gratuitement. Le premier « shuttle » est prévu pour novembre. Pour être dans le wagon, il faut que son projet soit open source et le soumettre au site en ligne efabless.com. Visiblement, la méthode de choix des projets retenus n’est pas encore bien définie ; mais si vous êtes retenu, vous aurez une réponse par courriel.

Il est temps pour LinuxFr.org de faire passer TapTempo dans une autre sphère que le simple programme en Brainfuck et de proposer un composant électronique TapTempoASIC !

Et pourquoi ne pas proposer un FPGA en 130 nm ? Même si aujourd’hui les FPGA sont plus proches du 40 nm, un FPGA open source comme le kFPGA de killruana, ça aurait la classe.

Comme j’en parlais sur LinuxFR, la société QuickLogic propose un kit de développement avec son microcontrôleur EOS S3. Micro qui a la prétention de n’utiliser que des logiciels libre pour son développement.

Le site web indiquait des «précommande». Je ne m’attendais donc pas à recevoir l’objet en moins d’une semaine, et sans frais de douanes !

Bref, si vous arrivez a trouver quelques amis pour faire une commande groupée (les frais de port pour la France sont plus cher que le kit lui même : $58 pour un kit à $49), n’hésitez pas ! Ça arrivera vite.

Au branchement sur l’usb-mini du kit, la led RGB s’allume à fond puis s’éteint progressivement en moins d’une seconde. Et … rien sur les messages kernel.

Il va falloir regarder tout ça de plus près et aller lire la doc. Le code source des exemples est dispo sur un github.

QuickLogic vient de faire une vidéo basique pour donner quelques trucs de mise en route.

Pour que le port série soit détecté dans le kernel il faut notamment appuyer sur le bouton reset. La led bleue va clignoter 5 secondes. Il faudra attendre à nouveau 5 seconde et le port /dev/ttyACM0 apparaîtra dans le dmesg :

[juin30 13:25] usb 3-3.1.2: new full-speed USB device number 17 using xhci_hcd

[ +0,100996] usb 3-3.1.2: New USB device found, idVendor=1d50, idProduct=6140

[ +0,000005] usb 3-3.1.2: New USB device strings: Mfr=0, Product=0, SerialNumber=0

[ +0,000575] cdc_acm 3-3.1.2:1.0: ttyACM0: USB ACM device

On peut ensuite simplement s’y connecter avec screen pour récupérer une invite de commande sur le micro :

$ screen /dev/ttyACM0 115200

####################

Quicklogic QuickFeather LED / User Button Test

SW Version: qorc-sdk/qf_apps/qf_helloworldsw

Jun 7 2020 12:04:51

##########################

Hello world!!

#*******************

Command Line Interface

App SW Version: qorc-sdk/qf_apps/qf_helloworldsw

#*******************

[0] >

De la on peut piloter les trois LED et lire le bouton, pour cela il suffit de se mettre en mode diagnostique:

[0] > red

ERROR: no such command: red

[0] > help

help-path: (top)

diag - QuickFeather diagnostic commands

exit - exit/leave menu

help - show help

? - show help

help-end:

[0] > diag

[1] diag > exit

[0] > help

help-path: (top)

diag - QuickFeather diagnostic commands

exit - exit/leave menu

help - show help

? - show help

help-end:

[0] > diag

[1] diag > help

help-path: diag

red - toggle red led

green - toggle green led

blue - toggle blue led

userbutton - show state of user button

exit - exit/leave menu

help - show help

? - show help

help-end:

[1] diag > red

[1] diag > blue

[1] diag > red

[1] diag > green

[1] diag > blue

[1] diag > userbutton

Not pressed

[1] diag > userbutton

Pressed

[1] diag >

[Dépèche écrite initialement pour LinuxFR]

Le lecteur assidu de LinuxFr.org sait déjà sans doute ce qu’est un FPGA. Rappelons‑en cependant brièvement la définition.

Les FPGA sont des composants constitués de « champs de portes programmables ». L’idée est de graver un certain nombre d’éléments logiques simples sous forme de matrice et de laisser au développeur le loisir de reconfigurer à l’infini les connexions entre ces portes. Une fois les connexions configurées, on se retrouve avec un composant numérique sur mesure qui ne ressemble à aucun composant disponible chez les fournisseurs classiques. C’est très pratique quand on a besoin d’architectures bâtardes, ou quand justement on développe un composant numérique : ça permet de reconfigurer à l’infini pour déverminer et évaluer les performances.

Pepijn de Vos a effectué un stage pour Symbiotic EDA. Et l’ingénierie inverse du GW1N était son sujet de stage. Il a rendu son rapport avant Noël sur GitHub et a publié le code source du projet Apicula.

Vous voulez en savoir plus, lisez la suite…

Parlons maintenant du grand drame des FPGA : ils sont complètement verrouillés car, pour reconfigurer ces fameuses connexions, il faut leur téléverser un fichier nommé bitstream qu’aucun constructeur de FPGA ne documente. Ce drame conduit les libristes que nous sommes à se taper des installations d’outils propriétaires particulièrement volumineux (surtout dans le cas de Xilinx et Altera) et pas toujours très stables. Tout ça pour générer le fameux bitstream.

Le format du bitstream n’est pourtant pas chiffré. Depuis plus d’une décennie, on sait qu’il est parfaitement possible d’en faire l’ingénierie inverse. Mais rien n’avait bougé jusqu’en 2015 quand Clifford (qui se prénomme maintenant Claire) Wolf a sorti sa suite open source pour le Lattice iCE40 : IceStorm. Le projet IceStorm avait pour but d’analyser toute la gamme des FPGA iCE40 pour en documenter le format du bitstream. Projet qui a parfaitement abouti et essaimé : toute la gamme des iCE40 est désormais accessible au moyen d’outils open source, ainsi que la gamme des ECP5 avec le Projet Trellis.

Presque tous les modèles de FPGA ont leur projet d’ingénierie inverse aujourd’hui. Tous ne sont pas terminés, loin s’en faut. Néanmoins, quelques‑uns avancent, comme le projet Apicula de Pepijn de Vos ciblant les FPGA du constructeur chinois Gowin. Dire que le projet Apicula est abouti serait un raccourci un peu rapide, il manque encore en effet un certain nombre de blocs à décoder. Cependant, il est possible aujourd’hui de réaliser un projet très simple (UNE LED QUI CLIGNOTE \o/) grâce au travail effectué.

Voici l’architecture du GW1N donnée dans la documentation du composant :

Oui, toi aussi, cher lecteur, tu te demandes bien l’intérêt de ce zoom. ;)

On voit différents éléments dans ce schéma, de la mémoire vive, des PLL pour générer les horloges, des multiplieurs câblés (DSP), des blocs d’entrées‑sorties (IOB) et surtout — ce que l’on voit le plus — des CFU (Configurable Function Unit).

Chez Gowin, le CFU est l’élément de base constitué ainsi :

Les deux éléments qui nous intéressent ici sont : la LUT (Look Up Table) et le REG (registre). Ces deux éléments sont la base de la logique synchrone.

Le registre recopie son entrée sur la sortie au front montant de l’horloge, la sortie restant stable le reste du temps.

La LUT, comme son nom anglais l’indique, est une table de vérité, qui, dans le cas de ce petit FPGA, comporte quatre entrées binaires et une sortie. La configuration du FPGA viendra remplir cette table de vérité pour réaliser une fonction logique. Le registre se trouvant derrière se charge ensuite de verrouiller le résultat au rythme de l’horloge.

Si l’on arrive à déchiffrer le bitstream pour pouvoir configurer ces LUT, ces registres ainsi que les blocs d’entrées‑sorties (IOB), alors on a (presque) gagné : on peut réaliser un composant simple mais fonctionnel.

Et c’est ce qu’a réalisé Pepijn de Vos, on peut donc dire qu’il a amorcé la libération du GW1N de Gowin !

Le projet n’est cependant pas terminé, il faut encore déchiffrer les autres blocs pour permettre l’utilisation complète du FPGA. Il faut également réussir à documenter les temps de propagation des signaux entre les différents blocs. L’information de ces temps de propagation permet au logiciel de placement routage (nextpnr, pour ne citer que le plus célèbre en libre) de faire son travail correctement.

Minute, papillon ! Dans un premier temps, il va falloir trouver une carte électronique munie d’un FPGA de Gowin. Nous allons ensuite nous servir des données déjà produites par le projet Apicula pour faire la synthèse avec Yosys, puis le placement‐routage avec nextpnr.

Pour le moment, deux kits de développement ont été utilisés dans le projet Apicula :

Nous allons tester avec le kit allemand TEC0117, mais le Tang Nano ne change pas grand’chose à la procédure (et il est moins cher).

On doit installer :

git clone https://github.com/YosysHQ/yosys.git

cd yosys make sudo make installice40 et ecp5 (les deux gammes de FPGA vraiment prises en charge par nextpnr) : git clone https://github.com/YosysHQ/nextpnr.git cd nextpnr/ cmake -DARCH=generic . make sudo make install Dans mon cas, j’ai dû forcer l’utilisation de Python 3.7 dans le fichier CMakeLists.txt : find_package(PythonInterp 3.7 REQUIRED); pour pouvoir exécuter les scripts en argument avec Python 3.7. git clone https://github.com/pepijndevos/apicula.git cd apicula ~/Documents/gowinsemi : Maintenant que nous avons les outils installés, lançons l’exemple générique du projet Apicula :

export GOWINHOME=/chemin/de/linstallation/gowin/IDE/ export DEVICE="GW1NR-9" # TEC0117 python dat19_h4x.py # makes $DEVICE.json python tiled_fuzzer.py # makes $DEVICE.pickle module top; wire clk; (* BEL="R29C29_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(1), .OUTPUT_USED(0)) clk_ibuf (.O(clk)); wire [7:0] leds; (* BEL="R1C8_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led7_obuf (.I(leds[7])); (* BEL="R1C8_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led6_obuf (.I(leds[6])); (* BEL="R1C10_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led5_obuf (.I(leds[5])); (* BEL="R1C10_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led4_obuf (.I(leds[4])); (* BEL="R1C11_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led3_obuf (.I(leds[3])); (* BEL="R1C11_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led2_obuf (.I(leds[2])); (* BEL="R1C12_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led1_obuf (.I(leds[1])); (* BEL="R1C12_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led0_obuf (.I(leds[0])); reg [25:0] ctr; always @(posedge clk) ctr <= ctr + 1'b1; assign leds = ctr[25:18]; endmodule Un habitué des LED qui clignotent en Verilog reconnaîtra tout de suite le compteur dans les dernières lignes (always, reg…) mais sera peut‑être perturbé par la déclaration des entrées‑sorties. Il faut juste avoir en tête que le projet n’est pas terminé et qu’il faut se taper le placement‐routage des entrées‑sorties « à la main », d’où les directives (* ... *) et les modules GENERIC_IOB(). $ cd generic $ bash simple.sh blinky.v # TEC0117 $ cd .. $ python gowin_pack.py generic/pnrblinky.json $ python gowin_unpack.py pack.fs $ yosys -p "read_verilog -lib +/gowin/cells_sim.v; clean -purge; show" unpack.v pack.fs que l’on peut téléverser dans le FPGA au moyen de l’utilitaire libre openFPGALoader maintenu par Trabucayre (Gwenhael Goavec‑Merou) : openFPGALoader -m -b littleBee pack.fs # FOSS programmer Parse pack.fs: Done erase SRAM Done Flash SRAM: [==================================================] 100.000000% Done SRAM Flash: FAIL Le FAIL est connu et vient d’une sombre histoire de somme de contrôle que openFPGALoader ne sait pas encore calculer et qu’Apicula ne fournit pas. Un ticket est ouvert sur le sujet dans le projet, Trabucayre sera ravi d’accepter des correctifs. Et les huit LED doivent clignoter. Enfin, disons plutôt qu’elles comptent en binaire. Pour voir la vidéo des LED clignotantes, c’est sur YouTube.

Comme nous avons des outils open source, il est possible de développer sur des ordinateurs à base d’architectures différentes de x86. Voici un petit exemple de téléchargement d’un bitstream sur Tang Nano au moyen d’un Raspberry Pi (architecture ARM). Le bitstream en question permet de piloter un écran à cristaux liquides.

Chose impossible à faire avec les Vivado, Diamond et autres Quartus.

Comme nous venons de le voir, le projet Apicula est encore très expérimental. Cependant, tous les ingrédients sont là et la preuve de fonctionnement est faite. Donc, à condition de mettre un minimum les mains dans le cambouis, on peut désormais générer des bitstreams pour les GW1Nx avec des outils open source.

Autant d’enthousiasme fait plaisir à voir. Pour contribuer, le mieux

est d’acquérir l’une des deux cartes citées dans cette dépêche et

d’installer le logiciel officiel de Gowin.

Ensuite, différentes commandes permettant de mettre le pied à l’étrier de l’ingénierie inverse sont données sur le README.md du projet Apicula.

Sinon, n’hésitez pas à laisser une issue sur le projet GitHub ou d’interpeller Pepijn directement sur le « silo social Twitter ». Pepijn est super content de voir des gens s’intéresser au projet et répond très vite.

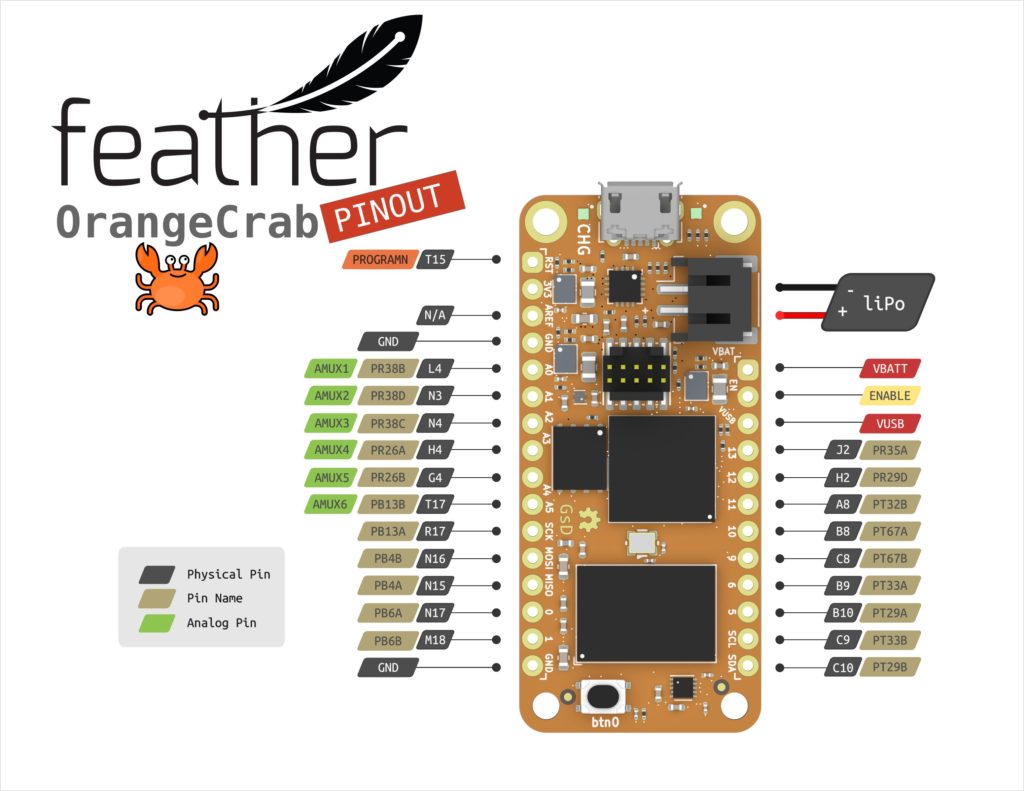

Ça y est, la carte à base d’ECP5 tant attendu est enfin disponible sur le site groupsget.

La carte qui est utilisable avec une chaîne de développement intégralement libre est constituée de:

Le tout pour des dimensions rikiki de 22.86mm x 50.8mm (0.9″ x 2.0″)

Ça fait quelques mois déjà que tout le monde l’attendait. Elle est disponible pour $99 à l’achat dès aujourd’hui.

Chisel is a hardware description language embedded in Scala language. Compared to VHDL/Verilog Chisel it’s a high-level language. With Chisel it’s easier to parametrize and to abstract your hardware. It’s the language used for all SiFive RISC-V cores and for Google Edge TPU.

What’s great with chisel that it generate Verilog sources for synthesis. And we can use this Verilog generated design for simulation or formal prove.

Simulation can be done in Scala with chisel.testers. But this tester is mostly under development project for the moment. And there is no test library for common busses and devices like SPI, Wishbone, AXI, PWM, …

CocoTB is a cosimulation testbench framework written in Python. Main advantage of CocoTB is that you write your testbench stimulis in python language. Python is really comfortable programming language. The other advantage of using CocoTB is that there is a growing library of modules available to test devices like SPI, Wishbone, USB, uart, … And its easier to use a library than to reinvent the wheel.

As an example we will use the ChisNesPad project (yes, same as formal prove article).

The directory structure is following :

/

|-- build.sbt <- scala build configuration

|-- src/ <- all chisel sources

| |-- main/

| |-- scala/

| |-- chisnespad.scala <- Chisel module we will test

| |-- snespadled.scala <- "top" module to test with

| tang nano (gowin)

|-- formal/ <- formal directory

|-- platform/ <- some usefull files for synthesis with

| final platform (gowin).

|-- cocotb/ <- python cocotb tests

|-- chisnespad/ <- test for chisnespad core

| |-- Makefile <- makefile to compile and launch simulation

| |-- test_chisnespad.py <- cocotb stimulis

|-- snespadled/ <- test for «top» project that toggle leds

| when push buttons

|-- Makefile

|-- test_snespadled.pyTo launch tests we needs following dependencies :

python -m pip install cocotb)Once all dependencies installed we can clone the chisNesPad project :

$ git clone https://github.com/Martoni/chisNesPad.gitThen launch simulation :

$ cd chisNesPad/cocotb/chisnespad/

$ make

make[1]: Entering directory '/home/fabien/myapp/chisNesPad/cocotb/chisnespad'

[...] lots of compilation lines [...]

/myapp/chisNesPad/cocotb/chisnespad/build/libs/x86_64:/usr/local/lib:/usr/local/lib:/usr/local/lib:/usr/local/lib:/usr/local/lib MODULE=test_chisnespad \

TESTCASE= TOPLEVEL=ChisNesPad TOPLEVEL_LANG=verilog COCOTB_SIM=1 \

/usr/local/bin/vvp -M /home/fabien/myapp/chisNesPad/cocotb/chisnespad/build/libs/x86_64 -m gpivpi sim_build/sim.vvp

-.--ns INFO cocotb.gpi gpi_embed.c:103 in embed_init_python Using virtualenv at /home/fabien/pyenv/pyenv37/bin/python.

-.--ns INFO cocotb.gpi GpiCommon.cpp:91 in gpi_print_registered_impl VPI registered

0.00ns INFO Running tests with Cocotb v1.2.0 from /home/fabien/pyenv/pyenv37/lib/python3.7/site-packages

0.00ns INFO Seeding Python random module with 1583180134

0.00ns INFO Found test test_chisnespad.always_ready

0.00ns INFO Found test test_chisnespad.double_test

0.00ns INFO Found test test_chisnespad.simple_test

0.00ns INFO Running test 1/3: always_ready

0.00ns INFO Starting test: "always_ready"

Description: None

VCD info: dumpfile ChisNesPad.vcd opened for output.

401300.00ns INFO Test Passed: always_ready

401300.00ns INFO Running test 2/3: double_test

401300.00ns INFO Starting test: "double_test"

Description: None

436000.00ns INFO Value read CAFE

470420.00ns INFO Value read DECA

471440.00ns INFO Test Passed: double_test

471440.00ns INFO Running test 3/3: simple_test

471440.00ns INFO Starting test: "simple_test"

Description: None

506140.00ns INFO Value read CAFE

507160.00ns INFO Test Passed: simple_test

507160.00ns INFO Passed 3 tests (0 skipped)

507160.00ns INFO *************************************************************************

** TEST PASS/FAIL SIM TIME(NS) REAL TIME(S) RATIO(NS/S) **

*************************************************************************

** test_chisnespad.always_ready PASS 401300.00 2.78 144519.92 **

** test_chisnespad.double_test PASS 70140.00 0.49 143736.56 **

** test_chisnespad.simple_test PASS 35720.00 0.25 144120.85 **

**************************************************************************************

507160.00ns INFO *************************************************************************************

** ERRORS : 0 **

*************************************************************************************

** SIM TIME : 507160.00 NS **

** REAL TIME : 3.52 S **

** SIM / REAL TIME : 144276.59 NS/S **

*************************************************************************************

507160.00ns INFO Shutting down...

make[1]: Leaving directory '/home/fabien/myapp/chisNesPad/cocotb/chisnespad'

(Note : I can’t find how to change width of code text in this #*/% wordpress )

And we can see wave form with gtkwave:

$ gtkwave ChisNesPad.vcd

All commands are described in the Makefile in directory chisNesPad/cocotb/chisnespad/.

The Chisel Module we test here is in directory src/main/scala/chisnespad/ and is named chisnespad.scala with following interfaces :

class ChisNesPad (val mainClockFreq: Int = 100,

val clockFreq: Int = 1,

val regLen: Int = 16) extends Module {

val io = IO(new Bundle{

/* SNES Pinout */

val dclock = Output(Bool())

val dlatch = Output(Bool())

val sdata = Input(Bool())

/* read/valid output */

val data = Decoupled(Output(UInt(16.W)))

})

//...

}The scala verilog generator driver is given at the end of file :

object ChisNesPad extends App {

println("Generating Verilog sources for ChisNesPad Module")

chisel3.Driver.execute(Array[String](), () => new ChisNesPad)

}This object will be called by SBT following command:

$ sbt "runMain chisnespad.ChisNesPad"This will generate the Verilog file named ChisNesPad.v in root directory. With following interfaces :

module ChisNesPad(

input clock,

input reset,

output io_dclock,

output io_dlatch,

input io_sdata,

input io_data_ready,

output io_data_valid,

output [15:0] io_data_bits

);

//...

endmoduleAs we can see, all bundled ports are kept but with little modification : dot ‘.’ are replaced by underscore ‘_’. clock and reset has been added and we can retrieve our decoupled signal io.data.{ready, valid, bits} -> io_data_{ready, valid, bits} .

With these changes in mind, we can read/write our chisel ports signals with CocoTB.

CocoTB tests are described in file test_chisnespad.py. This file describe a class to store all method and data for testing ChisNesPad Module then list cocotb test function :

# main class for all test

class ChisNesPadTest(object):

"""

"""

LOGLEVEL = logging.INFO

PERIOD = (20, "ns")

SUPER_NES_LEN = 16

NES_LEN = 8

def __init__(self, dut, reg_init_value=0xcafe, reg_len=16):

if sys.version_info[0] < 3:

raise Exception("Must be using Python 3")

self._dut = dut

#...

# all tests

@cocotb.test()

def simple_test(dut):

cnpt = ChisNesPadTest(dut)

yield cnpt.reset()

yield Timer(1, units="us")

dut.io_data_ready <= 1

#...

@cocotb.test()#skip=True)

def double_test(dut):

cnpt = ChisNesPadTest(dut)

yield cnpt.reset()

#...

@cocotb.test()

def always_ready(dut):

cnpt = ChisNesPadTest(dut)

yield cnpt.reset()

#...Here we see tree tests decorated with @cocotb.test(). The our module ChisNesPad is the Device Under Test (DUT) and is passed in test function arguments : dut.

To access input/output ports we just have to use dot on our dut object.

dut.io_data_ready <= 1 vread = int(dut.io_data_bits) countvalue = int(dut.countReg)It’s also possible to write register under the module, but be careful of the race condition when you doing that. It can be re-written by simulation with 0-delay.

All tests can be done with procedure describe above. But with Icarus as simulator we don’t get the waveforms.

It’s not easy to develop HDL without any waveform. To get waveform we can use another simulator that will generate the traces (mainly in VCD format) but Icarus is mature and free then it’s cheaper to use it.

The solution given in CocoTB documentation is to add following verilog code in top module :

`ifdef COCOTB_SIM

initial begin

$dumpfile ("ChisNesPad.vcd");

$dumpvars (0, ChisNesPad);

#1;

end

`endifWith this $dumpX() function we will records all signals under the file named ChisNesPad.vcd. If we had to add this code by hand each time we re-generate verilog from Chisel module, it would quickly become painful.

That why we use the tool cocotbify, included in package chisverilogutils.

$ cocotbify

Usages:

cocotbify.py [options]

-h, --help print this help

-v, --verilog verilog filename to modify (filename is used

as module name)

-o, --output filename output filenameThis tool will take a verilog source as input and generate an output with dumpvars code added for cocotb. In the example makefile the output name will be ChisNesPadCocotb.v. This file will be used by CocoTB and Icarus for simulation. VCD file can then be view with gtkwave:

$ gtkwave ChisNesPad.vcd

As we can see, it’s perfectly possible to use CocoTB framework for testing Chisel components. CocoTB has more library test modules available than chisel.tester and we can code in Python. Python is used by lots of peoples through the world and is less scary than Scala or SystemVerilog for hardware engineers that develop digital hardware.

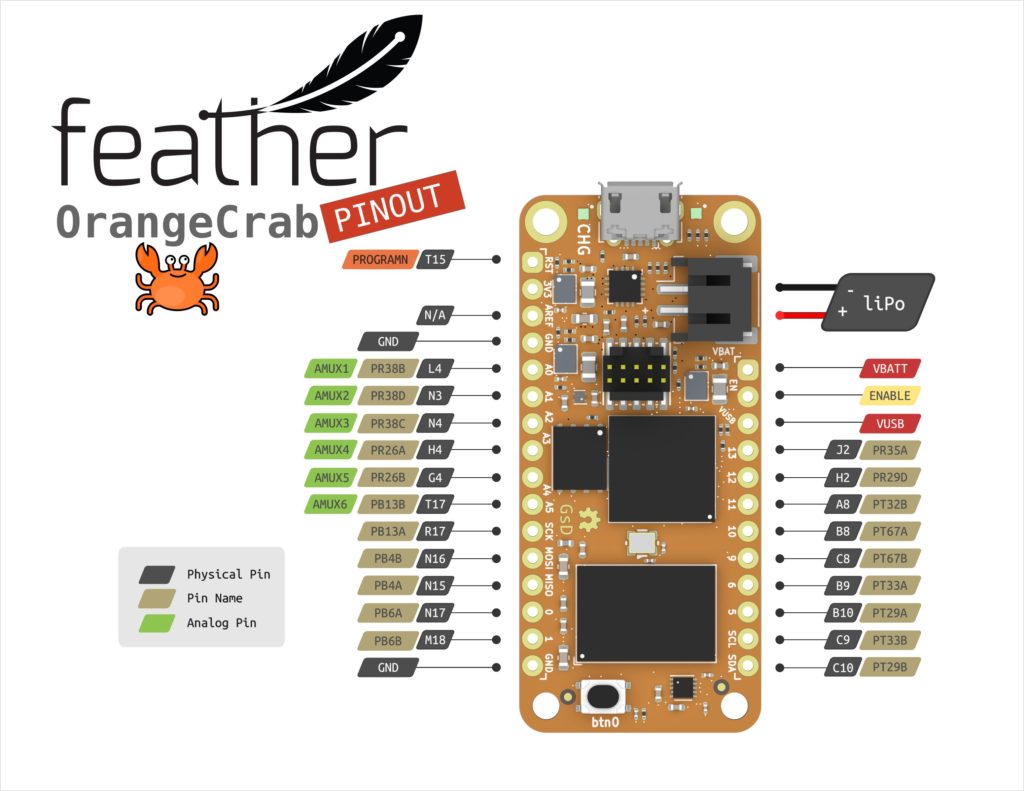

ECP5 is a great FPGA, it was reversed in Trellis, it’s bigger than ICE40 that was reversed before in icestorm project. And it have lots of cool stuff like

But ECP5 board available on the web are little bit expensive (if you have nothing to do with it ;). Even the OrangeCrab will be about 80$ minimum (but with DDR3 and USB on it).

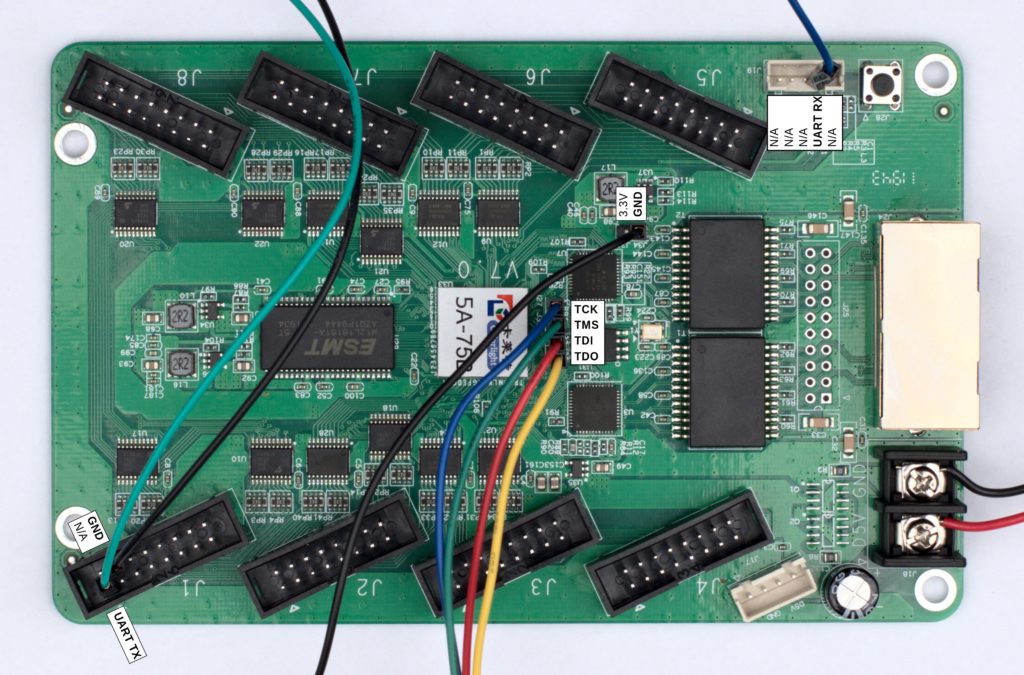

There is a rumor on the web that this leds display board include an ECP5 :

It’s really interesting, because this board cost only $15 ! With the dual SDRAM (M12L16161A) provided and its dual gigabit ethernet phy (Boardcom B50612D B1KMLG). For this low-cost price I order one of course.

I just received it and if we remove the sticker we see a Lattice ECP5 ( LFE5U-25F-6BG256C).

\o/ It’s a really lowcost ECP5 dev kit !

But without schematics. Mike Walter began to reverse it and document the board on its github project.

[Edit 1 March]

Anton Blanchard give the jtag+uart pinout on its twitter profile :

I configured the FPGA with this adapter from seeedstudio (7.6$), which is a simple FT2232 adapter.

ECP5 is available in openFPGALoader list as we can see :

$ openFPGALoader --list-fpga

IDCode manufacturer family model

0x81113043 lattice ECP5-5G LFE5UM5G-85F-8BG381

0x100381b Gowin GW1N GW1N-4

0x20f30dd altera cyclone 10 LP 10CL025

0x3620093 xilinx spartan7 xc7s15ftgb196-1

0x362d093 xilinx artix a7 35t xc7a35

0x900281b Gowin GW1N GW1N-1

0x1100581b Gowin GW1N GW1NR-9

0x13631093 xilinx artix a7 100t xc7a100

0x41111043 lattice ECP5 LFE5U-25F-6BG256C

0x612bd043 lattice MachXO3LF LCMX03LF-6900C

$ openFPGALoader -cdigilent --detect

idcode 0x41111043

manufacturer lattice

model LFE5U-25F-6BG256C

family ECP5

We can then load a simple blinker bitstream with openFPGALoader. But first, we have to synthesize one. Trabucayre gave me a simple blinker project I added to the BLP (Blinking Led Project).

This project require yosys, nextpnr and trellis to be installed. Installations instructions are given on trellis repository.

$ git clone --recursive https://github.com/SymbiFlow/prjtrellis

$ cd prjtrellis/libtrellis

$ cmake -DCMAKE_INSTALL_PREFIX=/usr .

$ make

$ sudo make installThen for next-pnr:

$ git clone https://github.com/YosysHQ/nextpnr.git

$ cd nextpnr

$ cmake -DARCH=ecp5 -DTRELLIS_INSTALL_PREFIX=/usr/ .

$ make

$ sudo make install

And finally Yosys

$ git clone https://github.com/YosysHQ/yosys

$ cd yosys

$ make

$ sudo make installThe blinker projet can be found on this github repository :

$ git clone https://github.com/Martoni/blp.git

$ cd blp/platforms/colorlight/

$ make

...

ecppack --svf blink.svf blink_out.config blink.bitThen, once JTAG is plugged we can download it with openFPGALoader :

$ openFPGALoader -cdigilent blink.bit

Open file blink.bit DONE

Parse file DONE

Enable configuration: DONE

SRAM erase: DONE

Loading: [==================================================] 100.000000%

Done

Disable configuration: DONEAnd see the orange LED blinking !

[this article will be edited as I progress]

Soon on groupgets.com according to Michel Welling.