Depuis quelques jours Quartus subit des plantages aléatoirement. Le logiciel se fige.

Le problème est connu, décrit ici avec son patch de résolution.

Depuis quelques jours Quartus subit des plantages aléatoirement. Le logiciel se fige.

Le problème est connu, décrit ici avec son patch de résolution.

Contrairement aux apparences, le logiciel de visualisation de Schéma/routage de Mentor (Maintenant siemens) PAD peut fonctionner sous Linux sans (trop) de problème.

Mais pourtant, la seule archive à télécharger sur le site officiel est un exe ?! Tout le monde sait qu’un fichier exe est un binaire exécutable pour Windows voir même pour DOS !

De fait, sous Linux, il est possible d’exécuter des exe grâce au vénérable wine. Ce logiciel n’est pas un logiciel franchouillard combattant la loi Évin.

Non ! c’est un émulateur windows qui permet d’exécuter des logiciels windows sous Linux.

En règle générale ça ne fonctionnne pas … Car l’émulation est toujours imparfaite, mais dans le cas du viewer Mentor/PAD le résultat est plutôt honorable et permet de visualiser des schéma/routage qu’on vous envoit.

Pour créer des cartes électroniques et/ou en éditer on préférera bien sur Kicad qui lui est parfaitement compatible avec Linux en plus d’être un logiciel libre.

On suppose que vous avez wine installé sur votre machine et que vous avez téléchargé l’archive de PADviewer . Il vous suffira ensuite de taper wine suivi du nom de l’archive :

$ wine PADSViewerVX.2.15_mib.exe

The most recent version of MIP is already installed in: c:\mentorgraphics\instal

l

MIP related file c:\mentorgraphics\install\tmp\FABIENM-TUXEDO-_32\ddinst32.exe w

as extracted successfully

MIP related file c:\mentorgraphics\install\tmp\FABIENM-TUXEDO-_32\vlhostid.exe w

as extracted successfully

MIP related file c:\mentorgraphics\install\tmp\FABIENM-TUXEDO-_32\ssidddp.sys wa

s extracted successfully

...

openjdk version "11.0.13" 2021-10-19

OpenJDK Runtime Environment Temurin-11.0.13+8 (build 11.0.13+8)

OpenJDK 64-Bit Server VM Temurin-11.0.13+8 (build 11.0.13+8, mixed mode)

053c:err:richedit:ReadStyleSheet skipping optional destination

053c:err:richedit:ReadStyleSheet skipping optional destination

053c:err:richedit:ReadStyleSheet skipping optional destination

053c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

0744:err:winediag:SECUR32_initNTLMSP ntlm_auth was not found or is outdated. Make sure that ntlm_auth >= 3.0.25 is in your path. Usually, you can find it in the winbind package of your distribution.

0744:err:ole:CoDisconnectObject apartment not initialised

075c:err:ole:CoDisconnectObject apartment not initialised

075c:err:ole:CoDisconnectObject apartment not initialised

Error getting install status ...Cela va lancer l’installeur graphique qui va décompresser l’archive avec quelques erreurs plus ou moins compréhensible à la micro$oft.

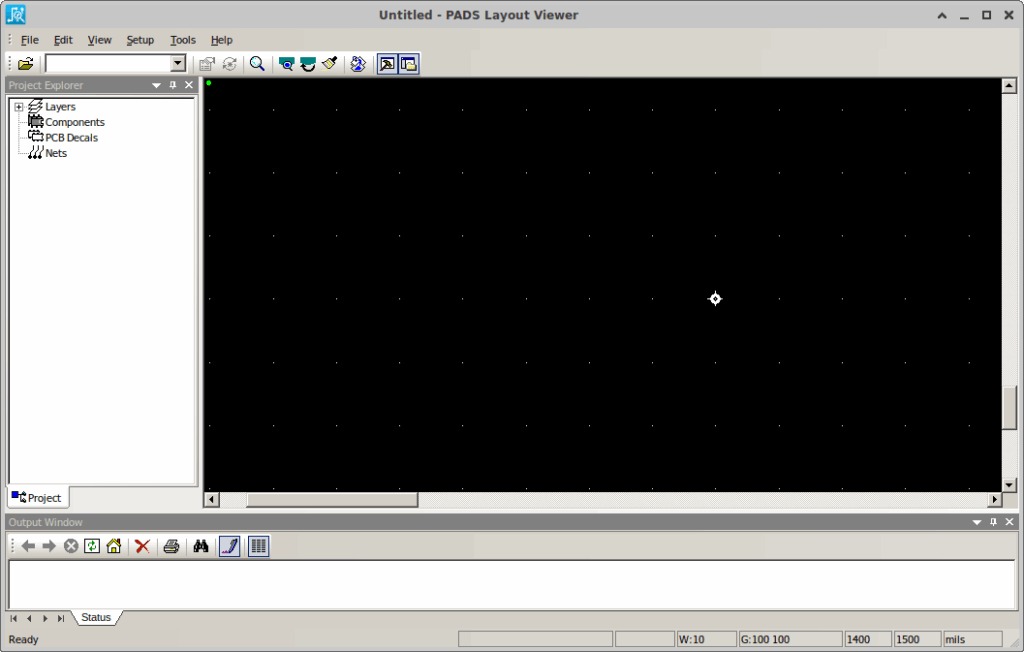

Une fois l’installation terminée, même avec erreur le programme se retrouvera installé dans votre home ~/.wine/drive_c :

~/.wine/drive_c/SiemensEDA/PADSVX.2.15Viewer/SDD_HOME/Programs/powerpcbviewer.exe

Programme que l’on pourra lancer, toujours avec wine pour visualiser son fichier pcb :

$ wine /home/user/.wine/drive_c/SiemensEDA/PADSVX.2.15Viewer/SDD_HOME/Programs/powerpcbviewer.exe

Pour le schéma (fichier sch) on utilisera powerlogicviewer.exe de la même manière.

Le viewer fonctionne assez bien, on arrive également à connecter le schéma avec le routage. Il y a quelques problèmes de police de caractères et parfois le logiciel plante, mais c’est un logiciel windows à l’origine, il y a des traditions à respecter 😉

[Dépêche parue initialement sur LinuxFR]

openFPGALoader est un utilitaire en ligne de commande, écrit en C++ et sous licence Apache 2.0. Il permet de configurer des FPGA de toutes marques. L’objectif du projet est de pouvoir prendre en charge tous les FPGA du marché ainsi que tous les adaptateurs et sondes de configuration.

Pour développer sur un FPGA, nous avons besoin d’un ensemble de logiciels et de formats spécifiques. La chaîne de développement sur FPGA peut se résumer par la figure ci-dessous:

L’architecture du composant est décrite dans un langage de description (HDL pour Hardware Description Language) matériel. Cette description est convertie en un schéma électronique (Netlist) par un procédé appelé «synthèse». Les composants de la Netlist sont ensuite placés dans la matrice du FPGA (placement) puis connectés ensemble (Routage) pour former le composant décrit au début.

Toutes ces informations sont ensuite décrites dans un fichier de configuration appelé bitstream (propriétaire). Et enfin, le fichier est transféré au FPGA pour le configurer.

À l’origine, toutes ces opérations sont réalisées par des logiciels privateurs, et les formats sont verrouillés. Quand on parle de libération des FPGA on aimerait bien sûr que toute la chaîne puisse être réalisée avec des logiciels libres et des formats ouverts. Mais le point le plus bloquant évoqué est souvent le format du bitstream, qui est LE maillon le plus critique de la chaîne jalousement gardé secret par (presque) tous.

Toutes ces étapes ont désormais des projets open source qui sont suffisamment avancés pour pouvoir développer sur FPGA librement. À condition de bien choisir le modèle.

On en oublie souvent la dernière étape consistant à télécharger le bitstream dans le FPGA. Pourtant cette étape est également dépendante du constructeur qui propose l’adaptateur à vil prix (souvent une sonde USB-JTAG). Et le logiciel est en général intégré au lourd IDE du constructeur (binaire x86) qu’il n’est pas toujours facile de configurer sur sa distribution Linux et encore moins sur une architecture exotique (raspberryPi, Risc-V, …).

Le dessein d’openFPGALoader est donc d’être « l’anneau pour les programmer tous ». Pour cela il faut :

Avec cette version 0.6.0, le logiciel peut être considéré comme mature. C’est tellement devenu une référence qu’il est même intégré dans quelques distributions Linux, dans buildroot. Le logiciel fonctionne également sur Mac et Windows avec cependant plus de problème du fait du passage par le pilote usb zadig.

C’est aujourd’hui un automatisme pour configurer un FPGA, de le tester d’abord avec openFPGALoader. Avant même d’utiliser l’outil constructeur. Le logiciel apporte un confort d’utilisation et de configuration qui n’a rien à envier aux autres.

Pour illustrer, un peu l’utilisation d’openFPGALoader, supposons que nous ayons notre bitstream permettant de faire clignoter la led de la carte Tang Nano 4K. L’avantage de cette carte est que l’adaptateur de programmation est inclus et que tout passe par le même port USB.

Une fois la carte branchée on peut commencer par détecter le FPGA avec --detect :

$ openFPGALoader --detect

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

index 0:

idcode 0x100981b

manufacturer Gowin

family GW1NSR

model GW1NSR-4C

irlength 8

Le format de bitstream pour les gowin possède l’extension fs, on peut le configurer directement en donnant simplement le nom du fichier en argument :

$ openFPGALoader led_test/project/impl/pnr/led_test.fs

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse led_test/project/impl/pnr/led_test.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

Flash SRAM: [==================================================] 100.00%

Done

SRAM Flash: Success

Et si le bitstream nous satisfait on l’écrira dans la mémoire « flash » avec l’option -f pour qu’il se reconfigure à chaque allumage.

$ openFPGALoader ide/gbhdmi/impl/pnr/gbhdmi.fs -f

write to flash

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse ide/gbhdmi/impl/pnr/gbhdmi.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

erase Flash Done

write Flash: [==================================================] 100.00%

Done

CRC check: Success

Les fichiers de configuration à télécharger dans le FPGA peuvent être assez volumineux pour certain gros FPGA. Les sondes de configuration n’étant pas toujours très rapide, il est intéressant de pouvoir envoyer le bitstream compressé.

Cette option est bien sûr supporté par openFPGALoader.

Plutôt que de prendre le nom du fichier bitstream en argument, il est également possible de récupérer un «flux» sur l’entrée standard:

cat /path/to/bitstream.ext | openFPGALoader --file-type ext [options]

Méthode très pratique si l’on souhaite configurer son FPGA via le réseau par exemple:

# Carte connectée au FPGA

nc -lp port | openFPGALoader --file-type xxx [option

# Ordinateur distant

nc -q 0 host port < /path/to/bitstream.ext

Et si vous trouvez que cette dépêche manque (scandaleusement) de TapTempo, sachez qu’openFPGALoader fonctionne très bien sur le FPGA ECP5 présent sur la carte colorlight pour y configurer le bitstream TapTempo en VHDL :

$ openFPGALoader taptempo.bit

Open file taptempo.bit DONE

Parse file DONE

Enable configuration: DONE

SRAM erase: DONE

Loading: [==================================================] 100.000000%

Done

Disable configuration: DONE

À l’heure où cette dépêche est mise sous presse, openFPGALoader a sorti une version mineure 0.6.1 (principalement pour réduire le nombre d’« assets » dans l’archive.

openFPGALoader est maintenant bien installé dans la constellation des logiciels libres pour développer sur FPGA. Même s’il n’a pas encore atteint la version 1.0, il est désormais tout à fait mature pour une utilisation en « production ». Il méritait bien une dépêche sur LinuxFR.

[Dépêche initialement parue sur LinuxFR]

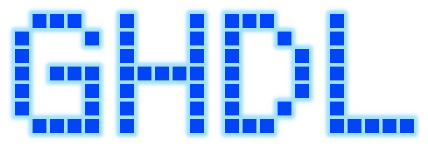

GHDL est un logiciel écrit en ADA permettant de faire l’analyse, la compilation, la simulation ainsi que la synthèse du VHDL. Le VHDL, quant à lui, est un langage de description matériel très utilisé dans le développement sur FPGA ou ASIC. À l’origine, GHDL est un « side-project » de Tristan Gingold lui permettant de se faire la main avec ADA.

GHDL est devenu l’outil indispensable pour faire de la simulation VHDL aujourd’hui. Après presque 20 ans de développement, voici que sort en version 1.0.0 le logiciel de simulation VHDL nommé GHDL. En prime, GHDL s’offre un nouveau logo:

Peu d’informations ont filtré sur cette sortie pour le moment. On peut soupçonner que ce soit une sortie anniversaire pour marquer les 20 ans du logiciel. Il n’en reste pas moins que GHDL est devenu un maillon indispensable dans l’écosystème opensource du monde FPGA et des ASIC.

Cette version 1.0.0 supporte désormais complètement les standards 1987, 1993 et 2002 du langage défini par l’IEEE. Le support de VHDL 2008 est noté comme partiel pour le moment.

Depuis quelques années, le développement du projet s’est accéléré et supporte de mieux en mieux les projets tierces comme Yosys bien sûr mais également CocoTB pour les testbenchs écrit en Python ainsi que les standards de vérification comme UVVM, OSVVM, VUnit issues du standard d’accelera.

Un support partiel d’un langage de PSL (Properties Specification Language) est également inclus. Il permet de décrire les propriétés du système pour faire de la vérification formelle.

Et surtout, il est possible de faire de la Synthèse. Certes, l’extension ghdl-yosys-plugin est encore en développement, mais l’exemple TapTempo l’a montré : Il est tout à fait possible de faire de la synthèse VHDL avec.

Cette version mature est surtout une occasion de mettre en valeur cet outil indispensable dans le monde du développement numérique (gateware).

[Dépêche publiée initialement sur LinuxFR]

C’est dans la soirée du 8 juillet que l’annonce est tombée : la version 1.4.0 de CocoTB est sortie. Cette nouvelle version est une belle évolution de Cocotb avec une bonne intégration dans le système de paquets de Python ainsi que l’abandon de la prise en charge de Python 2. On peut aujourd’hui dire que CocoTB est une alternative sérieuse pour écrire ses bancs de test HDL.

CocoTB est une bibliothèque de cosimulation permettant d’écrire (en Python) des bancs de test pour la simulation numérique HDL (Hardware Description Language). Historiquement, les deux langages de descriptions HDL que sont Verilog et VHDL embarquent tout le nécessaire pour écrire des stimuli permettant de tester le composant en simulation. Cela permet d’avoir un seul langage pour décrire le composant et le tester. Le simulateur exécutera tout cela sans problème.

Mais cela amène beaucoup de confusion entre la partie du langage utilisable pour la simulation uniquement et la partie « description du matériel ». Dans le cas de la partie « matériel » on parle alors de code « synthétisable ». Cette confusion entre du code synthétisable ou non est source de grandes frustrations au moment de passer à la synthèse. En effet, cette belle structure de données que l’on aura développée et testée aux petits oignons s’écroulera au moment de la synthèse quand on se rendra compte que le code n’est pas synthétisable. Il faudra tout reprendre.

Une des idées derrière CocoTB est donc de changer de langage pour la simulation, comme cela les choses sont claires : on utilise le VHDL ou Verilog pour la partie du composant qui est synthétisable, et on passe au Python pour le banc de test. Ce n’est pas le seul logiciel à proposer ce genre d’approche. Avec Verilator, par exemple, on va écrire toute la partie banc de test en C++ ou en SystemC. La partie synthétisable sera écrite en Verilog et convertie en un objet C++ par Verilator.

La seconde idée de CocoTB est de ne pas réinventer la roue en réécrivant un énième simulateur HDL. Ce qui évite également d’avoir à choisir son camp entre Verilog et VHDL ou les deux (simulation mixte). Non, CocoTB va se contenter de piloter les simulateurs disponibles sur le marché. Les simulateurs libres que sont GHDL, Icarus et Verilator sont naturellement pris en charge, même si dans le cas de Verilator c’est très récent. La plupart des simulateurs commerciaux le sont également, ce qui est un argument pour l’introduire dans son bureau d’étude. En effet, les managers sont en général moyennement chauds pour virer un logiciel acquis à grands frais. Et l’on peut continuer à profiter des interfaces proposées par notre simulateur habituel pour exécuter le simulateur, visionner les chronogrammes, faire de la couverture de tests, etc.

La version 1.4 de CocoTB introduit la gestion complète du simulateur Aldec Active HDL qui vient s’ajouter aux classiques de Cadence et de Mentor, Modelsim…

Un gros changement initié depuis quelque versions déjà est l’utilisation du mot clef async en lieu et place du yield et du décorateur @coroutine. Python 3 gérant désormais l’asynchronisme, CocoTB l’utilise et le prend désormais complètement en charge. L’exemple donné dans le courriel de la publication est le suivant :

@cocotb.test()

async def my_first_test(dut):

"""Try accessing the design."""

dut._log.info("Running test!")

for cycle in range(10):

dut.clk <= 0

await Timer(1, units='ns')

dut.clk <= 1

await Timer(1, units='ns')

dut._log.info("Running test!")Qui se serait écrit comme cela dans « l’ancien système » :

@cocotb.test()

def my_first_test(dut):

"""Try accessing the design."""

dut._log.info("Running test!")

for cycle in range(10):

dut.clk <= 0

yield Timer(1, units='ns')

dut.clk <= 1

yield Timer(1, units='ns')

dut._log.info("Running test!")Cette écriture restant cependant valable.

Le gros avantage de cette nouvelle écriture est de ne plus avoir a réinventer la roue avec des décorateurs inutiles. Avec async et await, on utilise des interfaces intégrées à Python 3, ce qui évite tout un travail de gestion.

CocoTB est, depuis maintenant un certain temps, partie intégrante du système de gestion de paquets de Python pip. Et vous pouvez dès à présent l’installer sur votre système via la commande pip install :

$ python -m pip install cocotb

# Pour celles et ceux qui ont installé la version précédente n’oubliez pas le --upgrade

$ python -m pip install --upgrade cocotbEt on peut vérifier la version grâce à la commande cocotb-config suivante :

cocotb-config --version

1.4.0

En plus de votre composant écrit en VHDL ou Verilog, deux fichiers supplémentaires sont nécessaires pour tester avec CocoTB : le Makefile et le script Python de test proprement dit.

Avec cette nouvelle version, le Makefile a encore été simplifié puisqu’il n’est plus nécessaire d’intégrer les en‑têtes C++. Ces en‑têtes sont nécessaires pour compiler les interfaces VPI/VHPI/FLI qui permettent de piloter les simulateurs. On compile désormais cette partie à l’installation de CocoTB. Dans les précédentes version, cette compilation ce faisait à chaque fois que l’on relançait les tests.

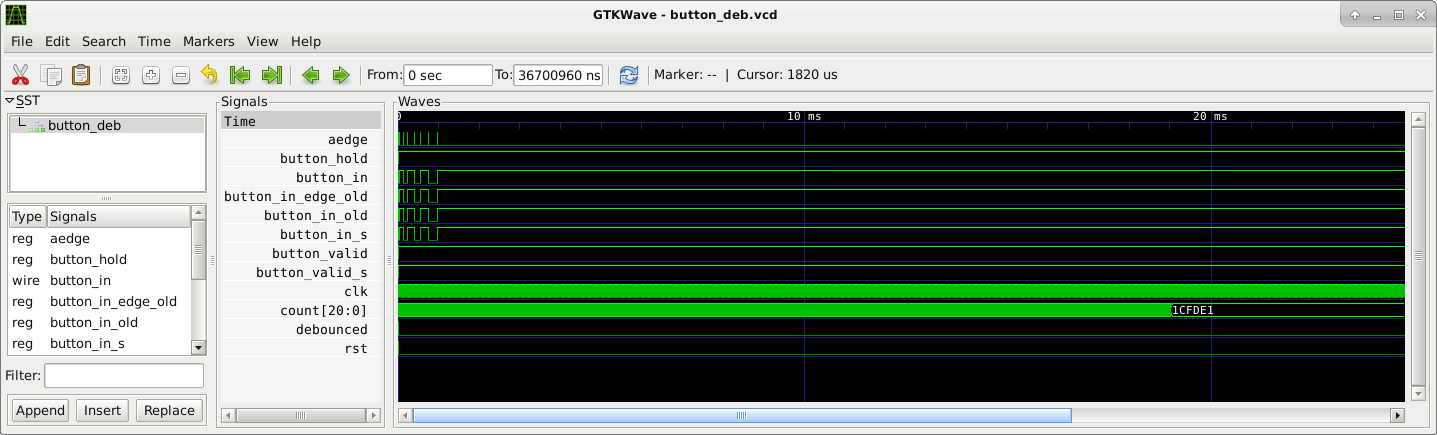

Si l’on prend l’exemple de l’antirebond en Verilog du Blinking Led Project, nous avons le Makefile suivant :

SIM=icarus # Nom du simulateur

export COCOTB_REDUCED_LOG_FMT=1 # Pour avoir des traces de log qui rentre dans l’écran

VERILOG_SOURCES = $(PWD)/../src/button_deb.v # Inclusion des fichiers HDL

TOPLEVEL=button_deb # Nom de l’entité

MODULE=test_$(TOPLEVEL) # Nom du script Python de test

include $(shell cocotb-config --makefile)/Makefile.simL’exemple est un composant permettant de ne pas compter les rebonds d’un bouton comme des appuis successifs.

Le script de test en Python se trouve dans le dépôt Git du projet et se nomme test_buton_deb.py. Pour le lancer, il suffit de se rendre dans le répertoire blp/verilog/cocotb/ et de taper make :

$ make

[...]

0.00ns INFO Running test!

0.00ns INFO freq value : 95000 kHz

0.00ns INFO debounce value : 20 ms

0.00ns INFO Period clock value : 10000 ps

0.02ns INFO Reset completeUn fichier de traces (chronogrammes) button_deb.vcd au format VCD est créé. Il peut être visionné en « temps réel » alors même que la simulation n’est pas terminée, grâce au visualiseur gtkwave :

$ gtkwave button_deb.vcd

Le projet CocoTB est chapeauté par la FOSSi foundation qui fournit le « chef de projet » Philipp Wagner ainsi que des moyens financiers pour faire tourner des machines virtuelles de tests ainsi que pour payer les licences des simulateurs commerciaux.

Les statistiques de modification de cette version sont les suivantes :

Ces chiffres montrent que CocoTB est un projet qui fédère désormais une grosse communauté. C’est un projet mature qui compte dans le paysage des logiciels libres pour le matériel (FPGA et ASIC).

[Dépêche initialement paru sur LinuxFR]

Pour configurer les différentes connexions des blocs de logiques contenus dans un FPGA il faut lui fournir un fichier de configuration appelé «bitstream». Quand on parle de libération des FPGA, on pense principalement à la publication de ces spécifications .

Jusqu’à présent, cette « libération » s’est faite, pour une poignée de FPGA (majoritairement Lattice), par ingénierie inverse. Donc jamais à l’initiative du constructeur, ce dernier n’ayant même pas toujours connaissance de projet d’ingénierie inverse à destination de ses produits. Et il faut aller fouiller dans d’obscurs fils Twitter et autre forums de bidouilleurs pour les découvrir.

Mais la libération s’accélère, et une petite société peu connue dans le monde du FPGA vient de lancer un produit basé sur des outils opensource pour le développement : l’EOS S3.

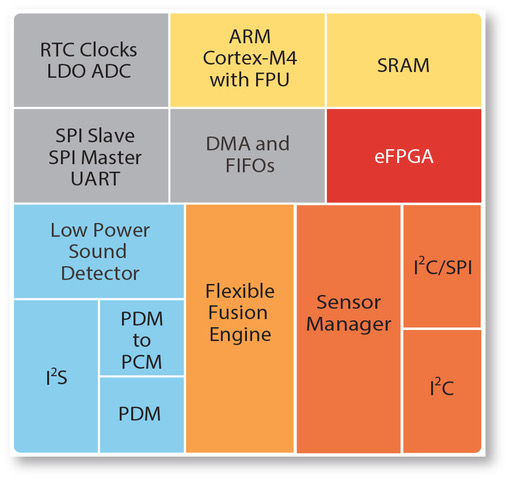

Comme on peut le voir dans le diagramme bloc ci-dessous, le produit est en fait un microcontrôleur Cortex-M4 qui possède une zone périphérique «de FPGA» appelé eFPGA.

La société Quicklogic a considéré que développer des logiciels de synthèse et de placement routage n’était pas son métier. Elle s’est donc « contenté » de l’adapter aux logiciels open source de la suite symbiflow.

Pour la première fois dans l’histoire des FPGA, nous avons donc une société qui affirme documenter son « bitstream » et qui propose des outils libres pour le développement. C’est un événement que beaucoup attendaient depuis des dizaines d’années !

Bon le (tout petit) FPGA ne concerne qu’une partie du composant. Mais c’est un bon début, et l’utilisation de logiciels libres reste la philosophie de la société pour le développement de ce produit. Comme dit dans les avantages de la fiche marketing du kit de développement :

« No more multi Gigabyte software installs, no more of the hassles associated with proprietary tools, no more vendor-specific hardware incompatible with the industry. »

La datasheet nous dit que la partie FPGA (celle qui nous intéresse ici) est composée de :

Alors certes, on est très très bas dans la gamme des FPGA du marché. Mais on peut déjà envisager faire des petites choses intéressantes avec. Surtout qu’il n’y a pas que le FPGA dans ce microcontrôleur.

Le kit est encore en phase de lancement, même s’il semble que certaines développeuses aient déjà reçu la carte pour faire des tests. Le tarif de $50 n’est pas prohibitif pour en envisager l’acquisition à des fin de tests. Les frais de port de $80 par contre posent problème, surtout s’il faut ajouter des frais de douane.

Bref, ça n’est pas du vaporware puisque les composants existent, mais il est pour l’instant difficile d’en dire plus concernant les outils. Dans tous les cas une nouvelle très rafraîchissante, et une accélération de la libération des FPGA qui fait plaisir !

L’entreprise qui est derrière ce nouveau produit est Antmicro. Une entreprise qui fait de la conception FPGA/ASIC à base de logiciel libre.

Il semble également qu’ils aient été aidé par google.

Et en plus du EOS S3, Quicklogic lance une gamme de FPGA «discret» : le PolarPro 3E. Également basé sur une chaîne de développement libre \o/

openFPGALoader is an open source C++ utility prog used to program/configure FPGA.

The goal of this project is to have one command line program to configure all types of FPGA regardless of probe or development kit is used.

For the moment the following FPGA are supported :

But the project is growing fast, no doubt that other FPGA will be supported soon.

Not only it’s easier to use than GUI, but it really fastest. With a MachXO3 6900 and digilent HS3 probe it take about 10 seconds on my computer :

$ time openFPGALoader -cdigilent_hs3 bitstream.jed

Open file bitstream.jed DONE

Parse file DONE

Enable configuration: DONE

SRAM erase: DONE

Enable configuration: DONE

Flash erase: DONE

Writing: [==================================================] 100.000000%

Done

Verifying: [==================================================] 100.000000%

Done

Write program Done: DONE

Disable configuration: DONE

Refresh: DONE

real 0m10,274s

user 0m0,728s

sys 0m1,676s

With official lattice diamond programer it take me 50 seconds.

Some tips for python HDL test module Cocotb.

Write:

clk.value = 1

dut.input_signal <= 12

dut.sub_block.memory.array[4] <= 2Read:

count = dut.counter.value

print(count.binstr)

print(count.integer)

print(count.n_bits)

print(int(dut.counter))See it under the official documentation.

Question asked on stackoverflow.

If you compile python yourself, don’t forget to add option --enable-shared at configure time (./configure --enable-shared)

$ virtualenv --python=/usr/local/bin/python3.7 ~/envp37

$ source ~/envp37/bin/activate

$ python -m pip install cocotbDo not forget to re-source your environnement each time you open a new terminal :

$ source ~/envp37/bin/activateThis is a template for declaring a class used for test in function @cocotb.test() :

import logging

from cocotb import SimLog

...

class MyDUTNameTest(object):

""" Test class for MyDUTName"""

LOGLEVEL = logging.INFO

# clock frequency is 50Mhz

PERIOD = (20, "ns")

def __init__(self):

if sys.version_info[0] < 3: # because python 2.7 is obsolete

raise Exception("Must be using Python 3")

self._dut = dut

self.log = SimLog("RmiiDebug.{}".format(self.__class__.__name__))

self.log.setLevel(self.LOGLEVEL)

self._dut._log.setLevel(self.LOGLEVEL)

self.clock = Clock(self._dut.clock, self.PERIOD[0], self.PERIOD[1])

self._clock_thread = cocotb.fork(self.clock.start())

# ....

@cocotb.test()

def my_test(dut):

mdutn = MyDUTNameTest()

mdutn.log.info("Launching my test")

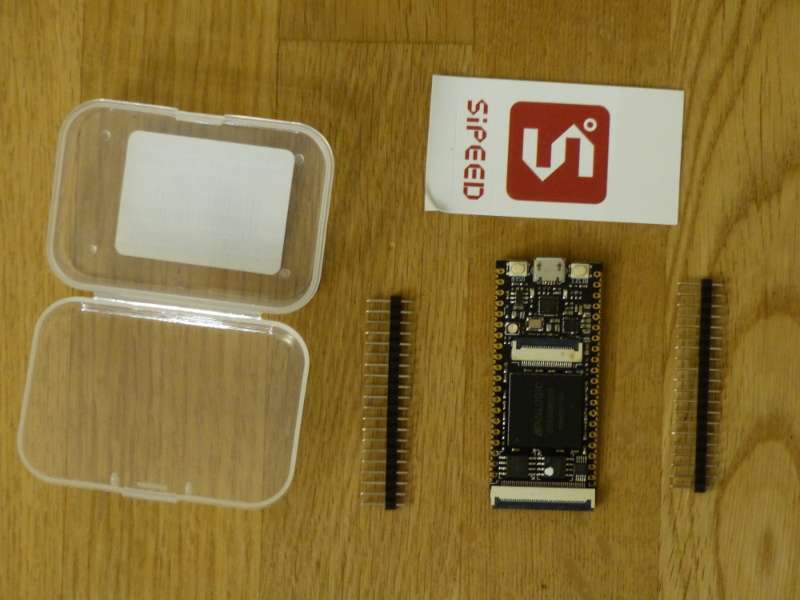

La société chinoise SiPeed propose un kit de développement permettant d’évaluer le FPGA chinois EG4S20BG256 produit par Anlogic. Le kit peut être commandé pour une vingtaine de dollars sur le site de vente en ligne Seeed spécialisé dans les kits de développement en électronique «grand public».

Au branchement du kit Debian/Linux détecte un convertisseur USB-JTAG de chez Anlogic:

$ sudo dmesg -c

[30017.300586] usb 3-2: new full-speed USB device number 5 using xhci_hcd

[30017.441796] usb 3-2: New USB device found, idVendor=0547, idProduct=1002

[30017.441801] usb 3-2: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[30017.441804] usb 3-2: Product: USB-JTAG-Cable

[30017.441807] usb 3-2: Manufacturer: Anlogic

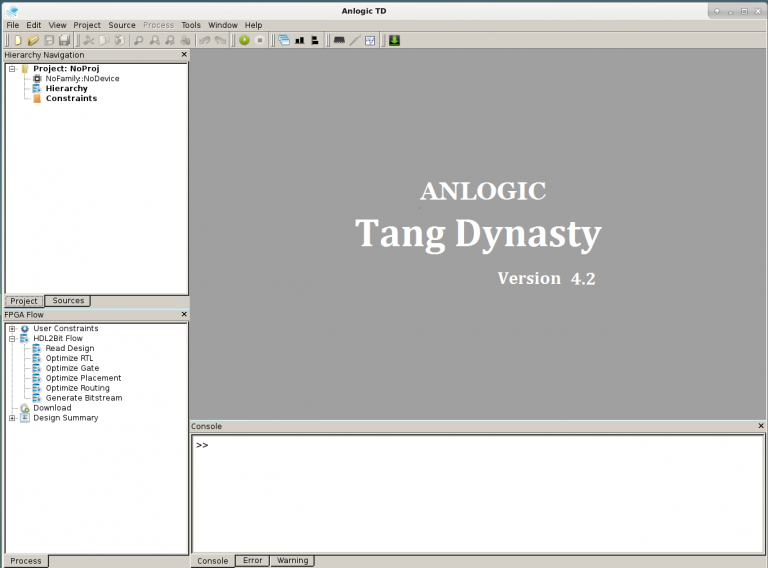

L’environnement de développement est disponible en téléchargement (~100Mo) sous forme d’une archive rar ici. Le fichier se décompresse avec la commande unrar:

$ unrar x ../TD_RELEASE_SEPTEMBER2018_RHEL.rar

Il faut ensuite mettre en exécutable le répertoire bin:

$ chmod +x bin/*

Et on peut ensuite lancer l’IDE:

$ cd bin ; ./td -gui

La fenêtre suivante s’ouvre alors :

C’est l’environement de développement le plus simple à installer que j’ai pu voir depuis que je bricole des FPGA. Même si la procédure d’installation est quand même étrange (un obscure .rar à télécharger puis à décompresser).

Pour synthétiser un premier design on va avoir besoin d’un minimum de documentation sur la schématique de la carte ainsi que sur le pinout du FPGA. On trouvera les schémas du kit en format pdf ici.

On trouve des exemples de code pour le kit sur github, notamment pour faire clignoter une led. La base du Hello World en électronique.

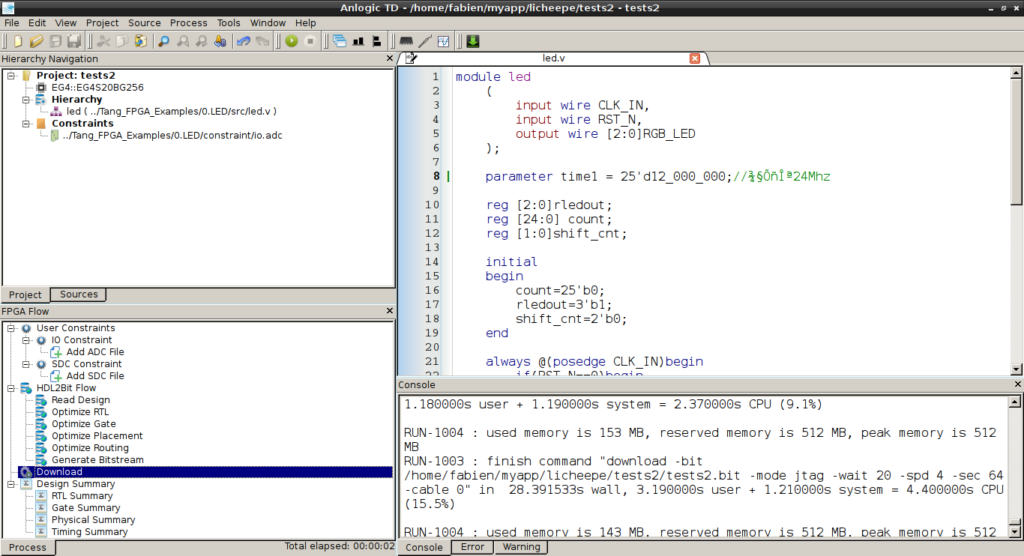

Pour tester la led qui clignote on crée un nouveau projet avec le fpga EG4S20BG256. On ajoute ensuite le source pour la led se trouvant dans le répertoire Tang_FPGA_Examples/0.LED/src/led.v

L’extension du fichiers de contrainte est en *.adc pour l’exemple de led le fichier se trouve dans le répertoire Tang_FPGA_Examples/0.LED/constraint/io.adc

Une fois les deux fichiers ci-dessus ajouté à notre projet on peut lancer la procédure complète pour générer le bitstream en double-cliquant sur l’icône «Generate Bitstream» dans l’encart «FPGA Flow» de l’ide.

La génération du bitstream est très rapide. Pour le télécharger ensuite dans le FPGA il faut bien sûr que le kit soit connecté à l’usb.

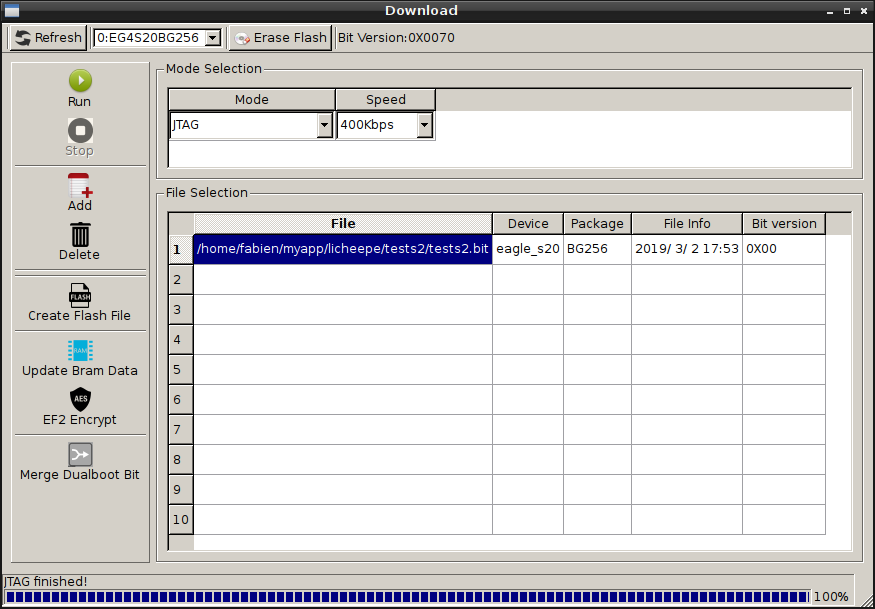

Le configurateur se lance en allant dans le menu Tools -> Download.

Chez moi j’ai du lancer l’ide en sudo pour éviter un plantage fatal, à ce moment. Le configurateur se présente comme ci-dessous :

Il faut ajouter le fichier bitstream au moyen du bouton de gauche «Add» puis cliquer sur la ligne du tableur pour «dégriser» le bouton «run», qui permet de télécharger le bitstream pour configurer le FPGA.

Pour conclure, je pensais beaucoup plus souffrir à mettre en route ce kit à la documentation majoritairement en chinois. Mais la note de blog de JAEB et le projet d’exemples sur github m’ont beaucoup aidé à faire clignoter cette led tricolore rapidement. À l’avenir il faudra regarder si ce FPGA est vraiment nouveau ou si ça n’est pas une copie d’un constructeur bien connu. On doit pouvoir vérifier ça avec le bitstream généré.

Au bout de quelques temps, la licence du logiciel expire. Il n’est plus possible de synthétiser avec. Un site chinois donne le truc pour que ça remarche. Pour éviter ce piratage, il semble être maintenant possible d’utiliser Yosys pour la partie synthèse !

This is just an install success story of Libero on Debian 9 (stretch). For the Risc-V contest, I recently acquired the Microsemi IGLOO2 development kit named FUTUREM2GL-EVB distributed by Futur-Electronic.

The development software for the IGLOO2 is named Libero and according to Microsemi, should works on Linux. But officially support only RedHat, CentOS and SuSE … not Debian. Microsemi provide a Linux installation guide to install it. It’s useful but should be adapted for Debian.

Download and install Libero

The first thinks to do is to download the installing file for Linux (and not the SP1 file which is only an update). Once downloaded we just have to launch it, if it’s not executable we can change rights with chmod command.

$ chmod 666 Libero_SoC_v11.9_Linux.bin $ ./Libero_SoC_v11.9_Linux.bin

An install windows will raise and we can follow directives.

Licensing

Once installed, we need to install the license. For that, we need to know our mac address :

$ ip addr show dev eth0 [...] link/ether 12:34:56:78:9a:bc [...]

The key that should be given to Microsemi is in upper case without ‘:’ :

$ ipython

In [1]: "12:34:56:78:9a:bc".replace(':','').upper()

Out[1]: '123456789ABC'

With this key we can then ask for a license file on microsemi website. The official Linux guide talk about license.dat file, but for me it was license.zip … Both are zip file in fact. We can then unflat it with unzip command:

$ unzip License.zip Archive: License.zip inflating: License.dat

The unflated file is a text file that should be edited with you text edito as explained in guide (page 6).

License server

The license server deamon must be downoaded on official microsemi website. Choose «Linux deamon» in table. It’s an archive of several binaries that should be unflated :

$ cd $ tar -zxvf Linux_Licensing_Daemon.tar.gz Linux_Licensing_Daemon/ Linux_Licensing_Daemon/actlmgrd Linux_Licensing_Daemon/lmgrd Linux_Licensing_Daemon/lmhostid Linux_Licensing_Daemon/lmutil Linux_Licensing_Daemon/mgcld Linux_Licensing_Daemon/snpslmd Linux_Licensing_Daemon/syncad Linux_Licensing_Daemon/synplctyd

Export shell variables

Before launching software, we have to export some paths in our .bashrc :

#Libero LIBERO_LICENSE_FOLDER=/home/giselle/flexlm LD_LIBRARY_PATH=/usr/lib/i386-linux-gnu/:/usr/lib/x86_64-linux-gnu/ # For Floating License from a License Server export LM_LICENSE_FILE=1702@gisellelaptop:$LM_LICENSE_FILE export SNPSLMD_LICENSE_FILE=1702@gisellelaptop:$SNPSLMD_LICENSE_FILE # <1702> is the port number # martonilp is the license server host name #For Node-Locked License export LM_LICENSE_FILE=$LIBERO_LICENSE_FOLDER/license.dat:$LM_LICENSE_FILE export SNPSLMD_LICENSE_FILE=$LIBERO_LICENSE_FOLDER/license.dat:$SNPSLMD_LICENSE_FILE export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:/usr/lib export DISPLAY=:0 export PATH=/opt/microsemi/Libero_SoC_v11.9/Libero/bin:$PATH

On my computer, Microsemi softwares are installed in /opt/ directory.

Launching Libero

First launch license server :

$ cd $./flexlm/lmgrd -c ~/flexlm/License.dat -log /tmp/lmgrd.log

Once license server launched we can run Libero :

$ libero /opt/microsemi/Libero_SoC_v11.9/Libero/bin/libero_bin: /opt/microsemi/Libero_SoC_v11.9/Libero/lib/libz.so.1: no version information available (required by /usr/lib/i386-linux-gnu/libpng16.so.16)

I had a little problem with libz provided with libero package, then I removed it and linked libz of my distribution :

$ apt-file search libz.so lib32z1: /usr/lib32/libz.so.1 lib32z1: /usr/lib32/libz.so.1.2.8 lib32z1-dev: /usr/lib32/libz.so zlib1g: /lib/x86_64-linux-gnu/libz.so.1 zlib1g: /lib/x86_64-linux-gnu/libz.so.1.2.8 zlib1g-dev: /usr/lib/x86_64-linux-gnu/libz.so ... $ cd /opt/microsemi/Libero_SoC_v11.9/Libero/lib $ mv libz.so.1 oldlibz.so.1 $ ln -s /lib/x86_64-linux-gnu/libz.so.1 libz.so.1

And then managed to launch it :

$ libero

But it’s unfortunately not finished.

First, when I tryied to synthesize I had this message in error window :

/opt/microsemi/Libero_SoC_v11.9/Synplify/bin/synplify_pro: 137: [: unexpected operator

/opt/microsemi/Libero_SoC_v11.9/Synplify/bin/synplify_pro: 151: [: !=: argument expected

/opt/microsemi/Libero_SoC_v11.9/Synplify/bin/synplify_pro: 324: /opt/microsemi/Libero_SoC_v11.9/Synplify/bin/config/execute: Syntax error: "(" unexpected (expecting ";;")

The problem come from the shell Debian uses by default :

$ ls -lha /bin/sh lrwxrwxrwx 1 root root 4 oct. 29 20:50 /bin/sh -> dash

This shell doesn’t work like bash and generate some error in synplify scripts. To solve it I simply changed the /bin/sh link to /bin/bash :

$ cd /bin/ $ sudo mv sh shold $ sudo ln -s bash sh

And I managed to synthesize my design.

…

But it’s not finished ! Once my bitstream generated I would like to download it on the IGLOO2 on kit. For that, we have to install correctly drivers for FlashPro5.

Directives are given in the official Microsemi Linux install guide, but udev syntax is false on Debian :

BUS=="usb",SYSFS{idProduct}=="2008",SYSFS{idVendor}=="1514",MODE="0660",GROUP="",SYMLINK+="FlashPro5"

BUS=="usb",SYSFS{idProduct}=="6001",SYSFS{idVendor}=="0403",MODE="0660",GROUP="",SYMLINK+="FTDI232"

Right rules are following :

# FlashPro5

SUBSYSTEM=="usb", ATTR{idVendor}=="1514", ATTR{idProduct}=="2008", MODE="0666", GROUP="plugdev"

SUBSYSTEM=="usb", ATTR{idVendor}=="0403", ATTR{idProduct}=="6001", MODE="0666", GROUP="plugdev"

Should be written in /etc/udev/rules.d/70-microsemi.rules file.

Then fully works and they lived happily and urged a lot of children