Une présentation de Cocotb à la conférence ORCONF 2015 du CERN.

Archives de catégorie : outils

Une nouvelle release d’icarus verilog est désormais disponible sur le ftp officiel.

Pour l’installer sous linux, rien de plus simple :

$ wget ftp://icarus.com/pub/eda/verilog/v10/verilog-10.0.tar.gz

$ tar -zxvf verilog-10.0.tar.gz

$ cd verilog-10.0/

$ ./configure

$ make

$ sudo make install

Vérifier la bonne installation avec :

$ iverilog -v

Icarus Verilog version 10.0 (stable) (v10_0)

Copyright 1998-2015 Stephen Williams

This program is free software; you can redistribute it and/or modify

it under the terms of the GNU General Public License as published by

the Free Software Foundation; either version 2 of the License, or

(at your option) any later version.

This program is distributed in the hope that it will be useful,

but WITHOUT ANY WARRANTY; without even the implied warranty of

MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

GNU General Public License for more details.

You should have received a copy of the GNU General Public License along

with this program; if not, write to the Free Software Foundation, Inc.,

51 Franklin Street, Fifth Floor, Boston, MA 02110-1301, USA.

iverilog: no source files.

Usage: iverilog [-ESvV] [-B base] [-c cmdfile|-f cmdfile]

[-g1995|-g2001|-g2005|-g2005-sv|-g2009|-g2012] [-g]

[-D macro[=defn]] [-I includedir]

[-M [mode=]depfile] [-m module]

[-N file] [-o filename] [-p flag=value]

[-s topmodule] [-t target] [-T min|typ|max]

[-W class] [-y dir] [-Y suf] source_file(s)

See the man page for details.

Projet IceStorm : le FPGA libéré !

Le jour du 27 mai 2015 sera à marquer d’une pierre blanche, en effet, c’est le jour où un FPGA a été libéré du joug des logiciels privateurs.

C’est le jour où Wolf Clifford a sorti une première version fonctionnelle du projet IceStorm permettant de synthétiser un design écrit en Verilog via Yosys et de faire le placement routage grâce à Arachne-pnr.

La conversion en bitstream et la programmation du chip se fait grâce aux utilitaires icepack et iceprog du projet IceStorm.

Pour l’instant le composant ciblé est le Lattice iCE40 HX1K-TQ144 pouvant être trouvé sur le kit d’évaluation lowcost (~$20) iCEstick.

Voici ci-dessous un petit howto rapide permettant de faire les manipulations se trouvant dans la vidéo de Clifford.

Icestorm howto

- Installation de Yosys

$ cd /opt $ git clone https://github.com/cliffordwolf/yosys.git $ yosys_deps="build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git mercurial graphviz xdot pkg-config python" $ sudo apt-get install $yosys_deps $ make config-gcc $ make $ make test $ sudo make install

- Installation d’IceStorm

$ sudo apt-get install libftdi-dev $ cd /opt/ $ mkdir icestorm $ wget http://www.clifford.at/icestorm/icestorm-snapshot-150526.zip $ unzip icestorm-snapshot-150526.zip $ make $ sudo make install

- Et enfin arachne-pnr

$ cd /opt/ $ git clone https://github.com/cseed/arachne-pnr.git $ make && sudo make install

- Synthèse, placement-routage, bitstream et programmation

Un exemple de «programme» est donné avec arachne-pnr dans le répertoire

example/rot. Cet exemple est composé du source en vérilog rot.v ainsi que du

placement des pin rot.pcf.

- Synthèse (Génération du blif)

$ cd /opt/arachne-pnr/example/rot/ $ yosys -p "synth_ice40 -blif rot.blif" rot.v

- Placement routage (Génération du txt)

$ arachne-pnr -d 1k -p rot.pcf rot.blif -o rot.txt

Le fichier généré rot.txt est la description finale du placement et du routage

du design dans le fpga. Cette description est parfaitement lisible en ascii

avec n’importe quel éditeur de texte.

Pour le télécharger dans le fpga nous devons le convertir en format binaire au

moyen de la commande «icepack» :

$ icepack rot.txt rot.bin

Nous avons un bitstream parfaitement compatible avec le ice40, il

nous faut maintenant le télécharger dans le fpga.

Et même pour cela, un logiciel libre est fourni : iceprog !

$ sudo iceprog rot.bin

On peut faire le tout en une seule ligne aussi si on veut :

yosys -p "synth_ice40 -blif rot.blif" rot.v;arachne-pnr -d 1k -p rot.pcf rot.blif -o rot.txt;icepack rot.txt rot.bin;sudo iceprog rot.bin

Et voila, bienvenue dans ce monde nouveau du FPGA libre !

Icarus vs Verilator

Plusieurs solutions de simulations s’offrent à nous quand on développe un composant en Verilog. On peut écrire le testbench en Verilog, de manière à être compatible avec la plupart des simulateurs du marché. Dans ce cas, le simulateur libre le plus célèbre est Icarus.

Mais la solution du «tout Verilog» est relativement lente en temps de simulation, et l’utilisation du langage Verilog est restrictive, en effet il n’est pas facile de s’approprier toutes les subtilités du langage.

C’est là que la solution de Verilator devient très intéressante. Verilator permet de convertir un modèle de composant écrit en Verilog synthétisable en un modèle C++. De cette manière, écrire le code du testbench revient à instancier notre composant dans un main() en C++ et à décrire nos tests avec toute la liberté qu’offre ce langage.

Mieux encore, il est possible d’écrire notre testbench en SystemC, et de profiter ainsi de cette librairie conçue pour la simulation de circuit numérique.

L’idée va être ici de mesurer le temps effectif de simulation de chacune de ses deux solutions. On se servira pour cela du composant d’antirebond du projet «blinking led project» (blp) disponible sur github.

Le composant synthétisable

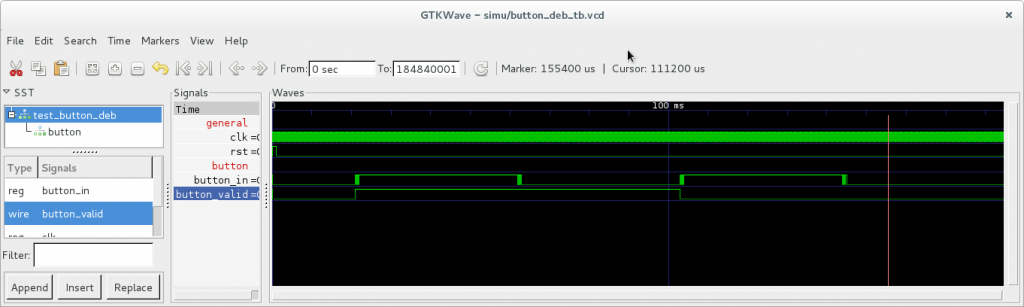

Le composant button_deb commute sa sortie button_valid à chaque front montant du signal d’entrée button_in. Pour que le fonctionnement soit un peu plus complexe qu’une simple commutation, et surtout pour bien coller au fonctionnement réel, le composant est muni d’un antirebond de 20 ms (par défaut). Quand le premier front survient, un compteur est déclenché et aucun autre front n’est pris en compte pendant 20 ms.

Voici ce que cela donne avec gtkwave:

Le testbench verilog (Icarus)

Tout comme en VHDL, un testbench en Verilog se présente sous la forme d’un module sans entrée/sortie.

La première chose à définir est le temps, avec la directive `timescale:

`timescale 1ns/100ps;Le premier chiffre indique le pas de simulation, cela correspondra au temps d’attente que l’on retrouvera tout au long du code avec l’«instruction» ‘#’. Le deuxième nombre indique la précision maximum.

Par exemple, pour simuler l’horloge à 95Mhz on écrira :

/* Make a regular pulsing clock. */

always

#5.263158 clk = !clk;

Mais comme la précision indiquée en début de code est de 100ps, seule le 5.2 sera pris en compte pour la simulation, ce qui dans notre cas est tout à fait suffisant.

La simulation de l’appui sur le bouton avec rebond se fait ensuite dans un process que l’on appel souvent «stimulis» par convention :

/* Stimulis */

initial begin

$display("begin stimulis");

$dumpfile("simu/button_deb_tb.vcd");

$dumpvars(1, clk, rst, button_in, button_valid, button);

$monitor("At time %t, value = %h (%0d)",

$time, button_in, button_in);

[...]

end

Le Verilog fourni tout un tas de primitive permettant de simplifier le debuggage. Notamment $display() et $monitor(), pour afficher du texte pendant la simulation. $display() ne fait qu’afficher du texte au moment où la fonction est appelée, alors que monitor va afficher le texte à chaque changement d’état de ses paramètres.

Les functions $dump* permettent de définir le format de fichiers des traces ainsi que les signaux a dumper. Dans ce cas précis on choisira le format vcd qui est un format non compressé, de manière à améliorer la comparaison avec verilator qui lui ne sait faire que du vcd. Mais cela génère vite de très gros fichiers, il sera préférable d’utiliser le format compressé lxt2, fst ou fsdb pour des simulations plus longues.

Pour factoriser un peu de code d’attente on décrit des tâches d’attentes wait_ms et wait_us :

/* some usefull functions */

task wait_us;

input integer another_time;

begin

repeat(another_time) begin

# 1_000;

end

end

endtask

task wait_ms;

[...]

Tâches qui seront appelées lors de la simulation des rebonds :

[...]

button_in = 1;

wait_us(`DEBOUNCE_PER_MS * 8);

button_in = 0;

wait_us(`DEBOUNCE_PER_MS * 8);

button_in = 1;

wait_us(`DEBOUNCE_PER_MS * 10);

button_in = 0;

wait_us(`DEBOUNCE_PER_MS * 10);

button_in = 1;

wait_ms(`DEBOUNCE_PER_MS * 2);

[...]

Pour lancer notre testbench avec Icarus, la première chose à faire est de compiler le code au moyen de la commande suivante :

iverilog -o simu/button_deb test/test_button_deb.v src/button_deb.v

Icarus va ainsi créer un binaire exécutable nommé simu/button_deb que l’on lancera avec les arguments de dumps:

vvp simu/button_deb -lvcd

Le fichier de traces (VCD) généré fait une taille vénérable de 752Mo et peut être visualisé avec gtkwave en l’indiquant simplement en paramètre de la commande :

gtkwave simu/button_deb_tb.vcd

Sur un Lenovo T430, la simulation prend 1 minute et 17 secondes, ce qui est tout de même relativement lent pour une simulation d’appui sur un boutton 😉

Voyons maintenant ce que nous donne Verilator.

Le testbench C++

Un testbench Verilator se présente sous la forme d’un main() C++. Dans le main() du testbench nous instancierons l’objet correspondant au model verilog transformé par verilator.

Pour cela nous devons donc convertir notre bouton_deb.v en C++ au moyen de la commande Verilator suivante :

verilator -Wall -cc src/button_deb.v --trace --exe test/test_button_deb.cpp

Cette commande va nous créer un projet avec le code source du modèle ainsi que le makefile pour compiler. Il suffira donc de se rendre dans le répertoire obj_dir et de faire «make» pour compiler le modèle.

Il ne nous restera plus qu’à instancier notre bouton dans notre testbench test_button_deb.cpp :

Vbutton_deb* top = new Vbutton_deb;

Ainsi que l’objet tfp pour les dump VCD:

VerilatedVcdC* tfp = new VerilatedVcdC;Pour simuler notre objet «top» il faut assigner des valeurs aux signaux d’entrées :

top->rst = 1;

top->button_in = 0;

top->clk = 0;

Puis évaluer les sorties avec la méthode eval() :

top->eval();

À chaque front d’horloge il faut donc changer la valeur de clk et évaluer :

top->clk = !top->clk;

top->eval();

Dans tout ce que nous venons de voir le temps n’intervient pas. En réalité, le temps n’est tout simplement pas géré dans les modèles Verilator, le modèle ne fait qu’évaluer les sorties en fonction des entrées, c’est à nous de gérer le temps comme nous le souhaitons.

Nous allons donc gérer le temps au moment du dump des signaux en lui indiquant le temps en argument:

tfp->dump(10);

Pour éviter d’avoir à taper tout ça à chaque fois on pourra créer une fonction «time_pass» qui fait passer le temps, avec un compteur global pour incrémenter le temps:

#define BASE_TIME_NS ((1000*1000)/(CLK_FREQ*2))

int base_time = 0;

/* the time is passing */

void time_pass(VerilatedVcdC *tfp, Vbutton_deb *top) {

top->clk = !top->clk;

tfp->dump(base_time*BASE_TIME_NS);

top->eval();

base_time++;

}

À l’image du testbench verilog, on pourra aussi créer des fonctions d’attente wait_ms et wait_us:

/* wait for us */

void wait_us(VerilatedVcdC *tfp, Vbutton_deb *top, int timeus) {

int wait_time = 0;

while((wait_time * BASE_TIME_NS) < (timeus * 1000)) {

wait_time++;

time_pass(tfp, top);

}

}

/* wait for ms */

void wait_ms(VerilatedVcdC *tfp, Vbutton_deb *top, int timems) {

int wait_time = 0;

while((wait_time * BASE_TIME_NS) < (timems * 1000 * 1000)) {

wait_time++;

time_pass(tfp, top);

}

}

Le code simulant les rebonds du bouton ressemble ainsi à s’y méprendre au code Verilog:

[...]

top->button_in = 1;

wait_us(tfp, top, DEBOUNCE_PER_MS);

top->button_in = 0;

wait_us(tfp, top, DEBOUNCE_PER_MS);

top->button_in = 1;

wait_us(tfp, top, DEBOUNCE_PER_MS * 5);

top->button_in = 0;

wait_us(tfp, top, DEBOUNCE_PER_MS * 5);

top->button_in = 1;

wait_us(tfp, top, DEBOUNCE_PER_MS * 8);

top->button_in = 0;

wait_us(tfp, top, DEBOUNCE_PER_MS * 8);

top->button_in = 1;

wait_us(tfp, top, DEBOUNCE_PER_MS * 10);

top->button_in = 0;

wait_us(tfp, top, DEBOUNCE_PER_MS * 10);

top->button_in = 1;

wait_ms(tfp, top, DEBOUNCE_PER_MS * 2);

[...]

Pour lancer la simulation on va d’abord compiler le tout :

make -C obj_dir/ -j -f Vbutton_deb.mk Vbutton_deb

Puis le lancer simplement comme un vulgaire binaire exécutable :

./Vbutton_deb

La simulation crée un fichier VCD de 654Mo que nous pouvons visualiser avec gtkwave.

Sur le même Lenovo T430 la simulation ne dure cette fois que 17 secondes, ce qui est très nettement plus rapide qu’Icarus !

Mieux, si on optimise le code à la compilation avec l’option -O3 :

verilator -Wall -cc src/button_deb.v --trace -O3 -noassert --exe test/test_button_deb.cpp

Le temps de simulation tombe à 3 secondes !

La rapidité d’exécution est telle que certain réussissent à faire «tourner» un soft-core avec son programme, à des fréquences allant jusqu’à la centaine de kilohertz.

Formidable !

C’est un peu l’expression que l’on a lors des premiers tests de verilator, pouvoir faire de la simulation 20 fois plus rapidement qu’Icarus semble formidable. Surtout quand cela passe par de la simplicité d’écriture du testbench en C++ ou SystemC.

Néanmoins il faut relativiser un peu notre ferveur, Verilator a encore un gros point noir: il ne gère pas le temps. Verilator n’est capable que de gérer des modèle Verilog synthétisable. Mais si ce code synthétisable inclu des primitives du constructeurs : RAM, Multiplieur, … et surtout PLL. Verilator ne sera pas capable de les simuler.

En ce qui concerne les Ram ou les multiplieurs cela ne pose pas trop de problème dans la mesure ou il est assez simple de les inférer. Mais pour les PLL cela devient bien plus compliqué, et je ne parle même pas des composants spécifique au constructeur (Bus serie, transceiver, core, …).

Ce «bug» a été répertorié il y 5 ans déjà mais pour l’instant personne ne semble s’être attelé à la tâche. D’après un des auteur de Verilator ajouter cette fonctionnalité devrait prendre quelques mois de programmation et de test. Mais cela vaudrait quand même le coup !

Alors qui s’y colle ?

vhd2vl: Convertir du vhdl en verilog

vhd2vl est un petit utilitaire écris en C (flex/bison) permettant de convertir du VHDL synthétisable en verilog. La page officiel présente la version 2.4, cette version ne compile qu’avec quelques modification sur une distribution récente.

Une version modifiée pour compiler sur debian jessie se trouve sur le github de Martoni. Pour l’utiliser il suffit de descendre le code avec git :

git clone git@github.com:Martoni/vhd2vl.git

Et faire un simple «make» dans le répertoire src/.

Pour convertir un fichier vhdl en verilog rien de plus simple (on pourra utiliser les exemples se trouvant dans les sources):

vhd2vl exemple.vhd > exemple.v

Le programme fonctionne plutôt bien à condition d’adapter son code vhdl de manière à générer un verilog correct.

En le testant sur mon «blinking led project» (blp), j’ai pu néanmoins constater quelques problèmes comme:

- Support hasardeux du type CONSTANT: Le type constant est converti en un «reg» ce qui n’est pas reconnu comme une constante par les logiciels de synthèse. On doit pouvoir modifier ça simplement pour qu’il génère un «localparam» par exemple.

- Pas de warnings sur les mots clef: Les mots clefs en vhdl ne sont pas les même qu’en verilog, vhd2vl ne râle pas quand il y a une variable en vhdl qui est un mot clef en verilog (par exemple avec le mot clef «edge»).

- Pas de support de l’underscore ‘_’ pour les nombres. En verilog/VHDL on peut mettre des séparateur pour les milliers histoire que ça soit plus lisible 1_000_000, vhd2vl ne comprend pas.

- Pas de support du type time (unité sec): bon ça c’est un peu tordu, car ça n’est pas synthétisable en l’état de toute manière.

Bref vhd2vl est un petit logiciel comportant peu de fichiers sources : en fait juste deux. S’il ne répond pas tout à fait à nos attentes il est très facile d’aller le modifier pour l’adapter.

Après discussion avec Larry, visiblement la version 2.4 sera la dernière car l’objectif est de l’intégrer au projet icarus verilog. Mais j’ai beau compiler la dernière version du trunk de icarus, je ne parviens pas à faire la même chose avec.

[EDIT 7 janvier 2016] Non non, vhd2vl n’est pas mort, Larry continu a le développer.

Compiler debit sous Jessie (debian)

Debit est un projet de logiciel permettant de faire du reverse sur les bitstreams des fpga Xilinx et Altera de manière à pouvoir ensuite faire de la synthèse libre.

Le projet était porté par Jean-Baptiste Note, mais le site de son projet ulogic.org reste inaccessible en permanence.

Le git du code est lui par contre accessible sur google code.

Le code n’ayant pas bougé depuis 2008 il a été nécessaire de faire quelques modification pour pouvoir compiler, ces modifications se trouvent sur le github de Martoni.

Pré-requis

Pour pouvoir compiler le projet sur Debian Jessie, il faut d’abord installer quelques packets:

sudo apt-get install xmlto xvfb valgrind glade build-essential

sudo apt-get install libgtk2.0-dev automake libcanberra-gtk-module

sudo apt-get install icoutils scrollkeeper gitGlade 2.12

Debit utilise une version antique de glade qui n’est plus disponible dans les packets debian, il faut donc l’installer à la main.

Pour cela il faut télécharger l’archive et la décompresser:

$ cd /opt/

$ wget http://ftp.gnome.org/pub/GNOME/sources/glade/2.12/glade-2.12.2.tar.gz

$ tar -zxvf glade-2.12.2.tar.gz

$ cd glade-2.12.2

Le code ne compile pas en l’état il faut modifier légèrement les includes. On peut le faire rapidement avec la commande suivante :

sed -i 's/gtkclist.h/gtk.h/g' glade/*.c

sed -i 's/gtkclist.h/gtk.h/g' glade/*.h

On peut alors le compiler et l’installer avec les commandes classiques:

./configure

make

make install

make clean

Debit

Prendre ensuite le trunk du git de martoni :

git clone git@github.com:Martoni/debit.git

Et compiler avec les commandes classique des autotools :

$ cd debit

$ ./autodo.sh

$ ./configure

$ make

Compiler Torc sous Debian Jessie

Prérequis :

sudo apt-get install libboost-all-dev

Descendre le svn (avec git c’est mieux) :

git svn clone https://svn.code.sf.net/p/torc-isi/code/trunk torc

Faire un premier «make» dans src/, ce qui va créer un fichier nommé Makefile.local. Ouvrir ce fichier et ajouter les path vers boost :

BOOST_INCLUDE_DIR = /usr/include/boost/

BOOST_LIB_DIR = /usr/lib/

Faire un make (toujours dans src/) :

$ make

La configuration converti tous les warning en erreur (-Werror), et comme il reste des warnings visiblement dans le svn on arrive pas à tout compiler. Pour compiler malgré tout, virer l’option dans le fichier src/torc/Makefile.targets (ligne 59):

-Werror \

Torc est un logiciel libre permettant de générer les bitstreams pour les fpga Xilinx:

Compiler GHDL avec ses petites mains

GHDL est le plus avancé des simulateurs libre pour le VHDL. GHDL est déjà intégré dans de nombreuses distributions, un simple «apt-get install ghdl» fonctionne sur une ubuntu ou une debian (wheezy).

Cependant, il se peut que nous souhaitions utiliser la dernière version en date de ghdl (0.32). Il se peut aussi que ghdl ne soit pas encore intégré à notre distribution préférée (c’est le cas de Debian Jessie), auquel cas nous aurons besoin de compiler l’outil depuis les sources.

dépendances

Les paquets suivants doivent être installé au préalable :

$ apt-get install gnat mercurial

Récupérer les sources

Les sources se trouvent sur sourceforge et utilise mercurial comme gestionnaire de version:

$ cd /opt/

$ hg clone http://hg.code.sf.net/p/ghdl-updates/code ghdl-updates-code

Nous allons aussi avoir besoin des sources de gcc:

$ wget ftp://ftp.uvsq.fr/pub/gcc/releases/gcc-4.9.2/gcc-4.9.2.tar.bz2

Une fois les sources téléchargées il faut générer une archive que nous décompresserons ensuite dans les sources de gcc.

$ cd ghdl-updates-code/translate/gcc

$ ./dist.sh sources

Installation du vhdl dans gcc

On décompresse tout d’abord les archives de ghdl fraichement générée et de gcc:

$ cd /opt/

$ tar -jxvf ghdl-updates-code/translate/gcc/ghdl-0.32dev.tar.bz2

$ tar -jxvf gcc-4.9.2.tar.bz2

Puis on copie le code du plugin vhdl dans gcc

$ cp -R ghdl-0.32dev/vhdl gcc-4.9.2/gcc/

Compilation

Pour compiler il nous suffit maintenant de nous rendre dans le répertoire de gcc puis de faire un ./configure, make, make install:

$ cd gcc-4.9.2/

$ mkdir /opt/ghdl/

$ ./configure --enable-languages=vhdl --disable-bootstrap --prefix=/opt/ghdl/

make CFLAGS="-O"

L’ajout de «–prefix=/opt/ghdl» permet d’éviter de péter son installation de gcc en installant ghdl dans un autre endroit.

Pour utiliser notre version compilée de ghdl il suffit donc de l’appeler en donnant le bon path :

$ /opt/ghdl/bin/ghdl --help

usage: /opt/bin/ghdl COMMAND [OPTIONS] ...

[...]

Quels outils libres pour FPGA ?

Une présentation faite aux rmll de strasbourg en 2011: