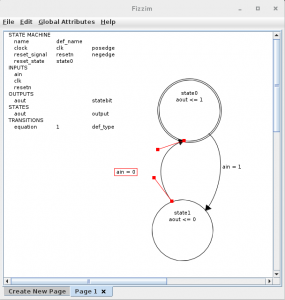

Fizzim est un petit logiciel graphique écrit en Java permettant de dessiner des machines d’états. Ce qui le différencie des autres logiciels de «dessin» c’est que Fizzim est capable de générer le code Verilog et/ou VHDL synthétisable correspondant.

Installation

L’archive est disponible sur le site officiel. Pour l’installer sous Linux, il suffit de la télécharger et de la dezziper dans le répertoire de son choix :

$ mkdir fizzim $ cd fizzim $ wget wget http://www.fizzim.com/mydownloads/fizzim_520.zip $ unzip fizzim_520.zip

La documentation est disponible sous la forme d’un pdf. C’est un programme écrit en java il faut donc lancer «l’executable» avec la machine virtuelle java :

$ java -jar fizzim_v14.02.26.jar

Fizzim enregistre ses projets avec un format *.fzm. Pour générer du code Verilog ou VHDL il faut utiliser le script perl fourni :

$ perl fizzim.pl < test.fzm > test.v

Pour le VHDL faire:

$ perl fizzim.pl -language VHDL < test.fzm > test.vhd

Un petit programme qui ne paye pas de mine mais qui est bien utile, surtout que le développement FPGA fait un usage intense des machines d’états.