Le FLF a été fondé a une époque obscure où il n’existait (quasiment) pas de solution open-source pour travailler sur des FPGA. Seul un petit village d’irréductibles simulateurs comme icarus, ghdl ou verilator maintenaient un semblant de liberté dans cet océan de sombre verrouillage. Il y avait bien VTR et Alliance, mais ils restaient très universitaire et un peu trop centré sur les ASIC.

Puis est arrivé Yosys le logiciel libre de synthèse Verilog accompagné du reverse engineering de l’ICE40 avec Icestorm. Ont suivis Apicula pour les Gowin, X-Ray pour les Xilinx série 7 ou Trellis pour les ECP5 (Voir le tableau des projets de reverse sur le FLF).

Et pour boucler la boucle de développement, le logiciel libre de placement routage nextpnr a émergé ainsi que le logiciel de configuration universelle openFPGALoader.

Toutes ces initiatives ont énormément gagnées en qualité et en crédibilité depuis 3 ou 4 ans et sont en passe de devenir les références dans le monde du FPGA.

À ces nouvelles très réjouissantes se sont ajouté les annonces de plusieurs mise en production de FPGA avec les outils open-source supportés officiellement par les constructeurs. On pense notamment à :

- Quicklogic et son microcontrôleur EOS S3 basé sur un cœur Cortex-M4 couplé à une «zone» de FPGA utilisable intégralement avec des logiciels open source.

- CLEAR: un projet plus anecdotique consistant à générer un FPGA à partir de l’outil open source openFpga et à l’intégrer à la Caravel de la société eFabless pour la graver en 130nm. Pour le coup les outils pour développer le FPGA sont opensource ainsi que les outils pour développer sur le fpga.

- CologneChip et son GateMate: un FPGA à l’architecture assez original notamment pour la partie calcul/dsp mais qui se défend assez bien niveau taille.

Avec toutes ces nouvelles on aurait pensé que cela allait se calmer et que l’on aurait le temps de digérer et faire clignoter quelques LED avant de passer à une vitesse encore supérieure.

ERREUR !

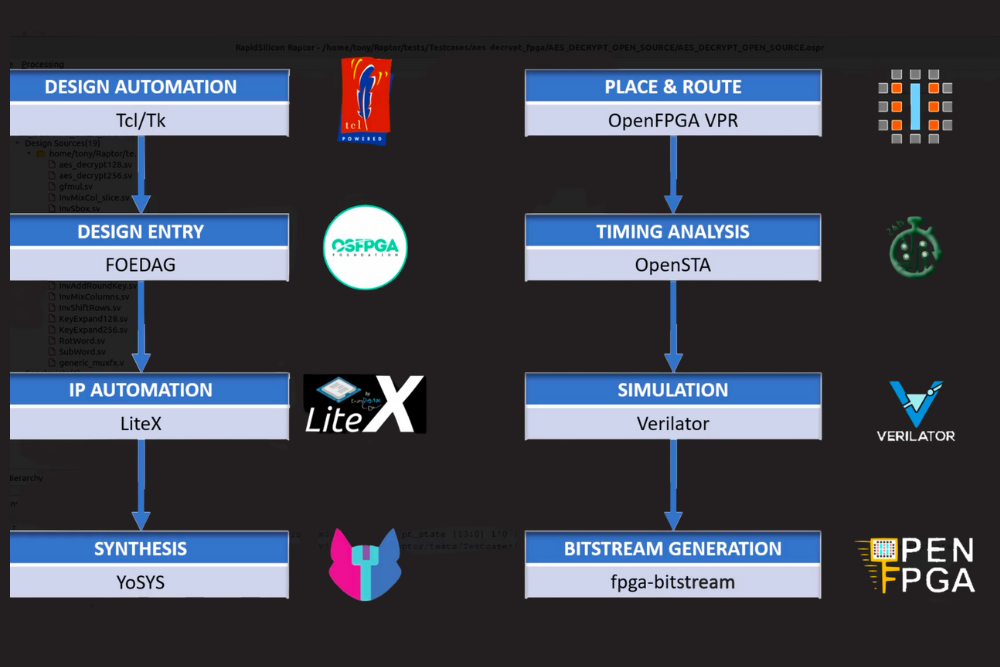

C’était sans compter sur cette société créé en 2020 (et oui toute neuve) et son annonce de sortie du projet Gemini (un poil prétentieux tout de même pour le nom 😉 de faire un SoC haute performances en se basant sur des outils open sources, et oui même pour la fabrication du FPGA. En parallèle du développement silicium, RapidSilicon développe un IDE open source nommé Raptor se basant sur tout un tas de logiciels libres cité au début de cet article :

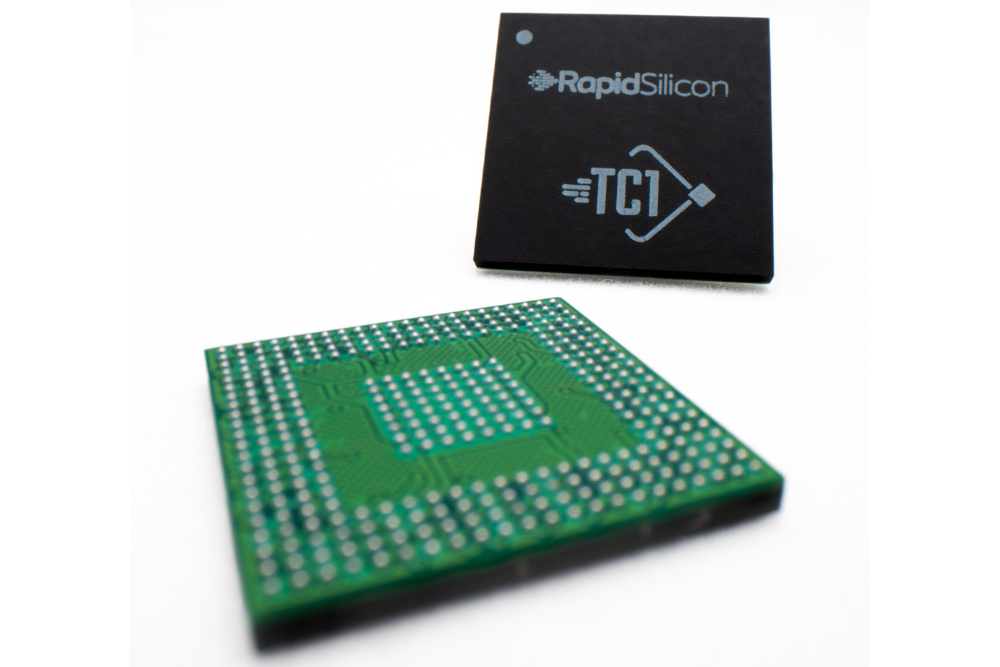

Un premier échantillonnage de composants en 16nm est déjà sorti des fonderies de TSMC et nous rassure sur la réalité du produit. Nous ne sommes pas dans le cas d’une société qui fait des annonces «vaporware» juste pour faire des levées de fond.

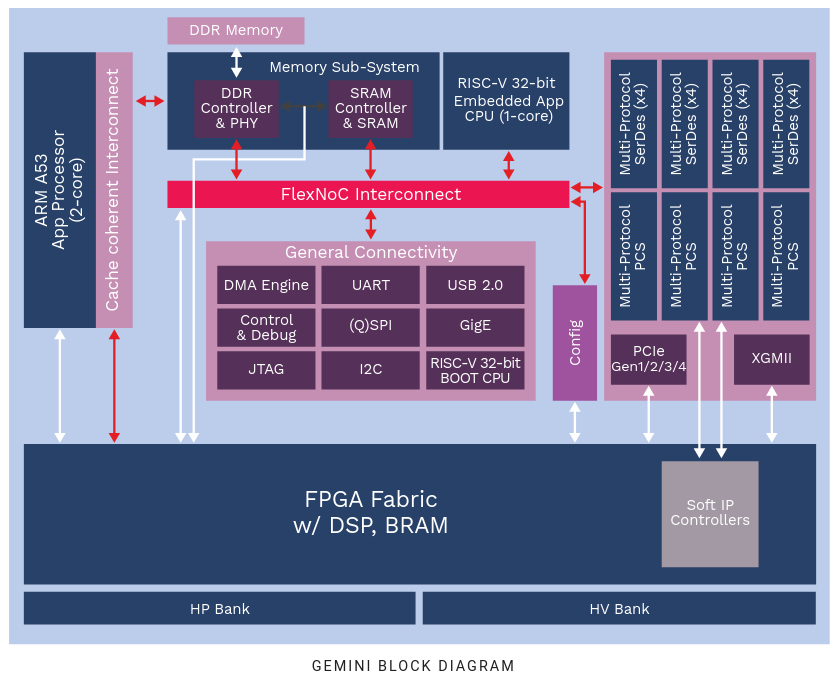

L’architecture du prototype est donnée dans la figure suivante:

On est donc dans le cas d’un gros SoC-FPGA avec les caractéristiques suivantes :

- Arm A53 Dual-Core

- contrôleur de DDR4

- «Petit» core Risc-V 32bit pour le temps réel et la supervision

- Les ports habituels d’un SoC : UART, USB, SPI, I²C, …

- Du PCIe Gen4, XGMII (pour le réseau)

- Des liens serdes (très) rapide jusqu’à 16Gbits/s

- La zone FPGA n’est pas énorme, mais se défend face aux petit Zynq par exemple :

- 50-75K LUT (6 entrées)

- Blocks DSP (combien ?)

- Block de Ram double port 18kb (Combien ?)

Toutes ces parties sont liée ensemble au moyen d’un bloc d’interconnexion nommé FlexNOC.

Alors ?

Xilinx doit-elle trembler avec son Zynq ? et Microsemi avec son PolarFire SoC ?

L’avenir nous le dira, hâte de voir la suite 🙂