- Vivado 2023 : 55Go

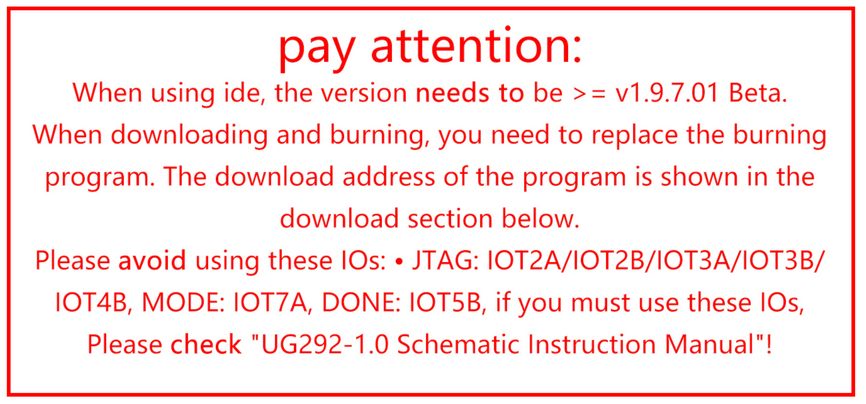

- Quartus Pro 24.1: 67 Go

- microchip 2023.2 (polarfire, smartfusion et igloo): 38Go

- Efinity 2023.2: 2.2 Go

- Radiant 3.0: 2.4Go

- xc7 f4pga : 8.7Go

- qorc (QuickLogic) : 4.5Go

- Gowin_V1.9.9: 1.6Go

- GateMate (CologneChip) : 73Mo

Archives par mot-clé : gowin

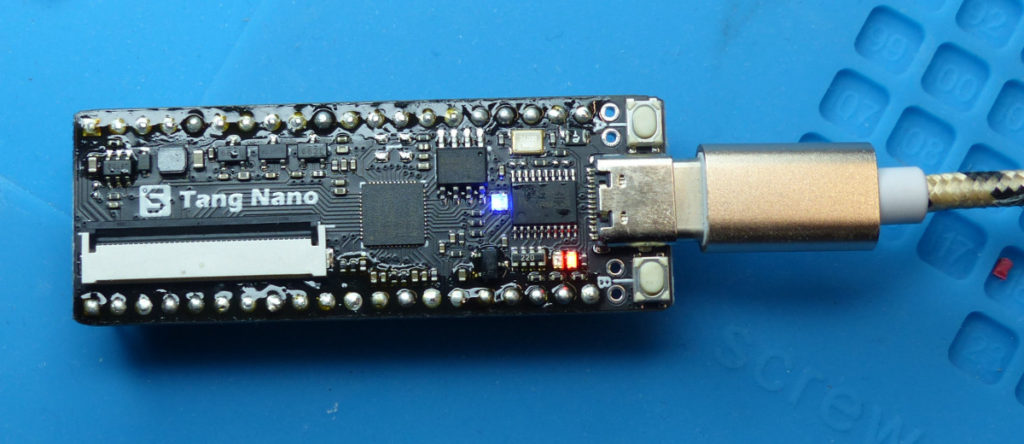

Déballage de la TangNano9k

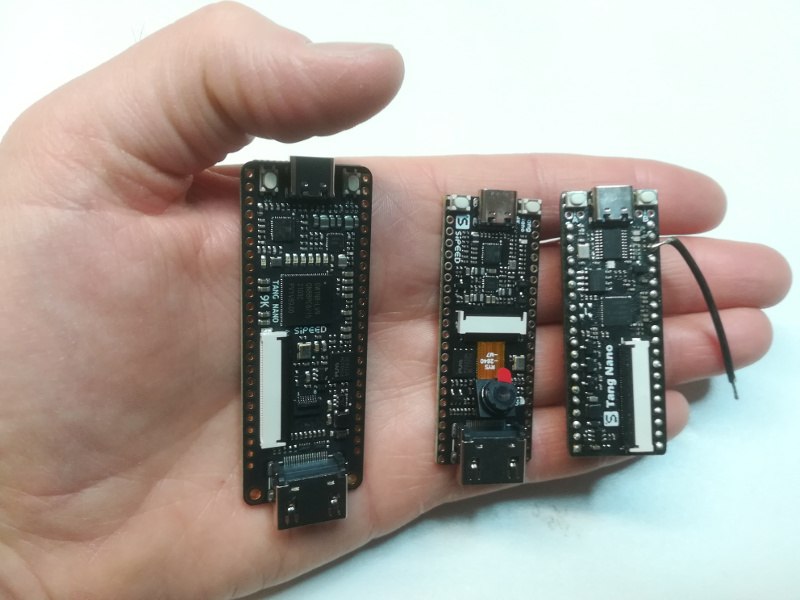

Ça y est, le colis contenant la carte de développement Tang Nano 9k est arrivé. Contrairement à la TangNano4k je ne l’ai pas reçue rapidement, il a fallu attendre environ deux mois. Mais elle est bien là maintenant.

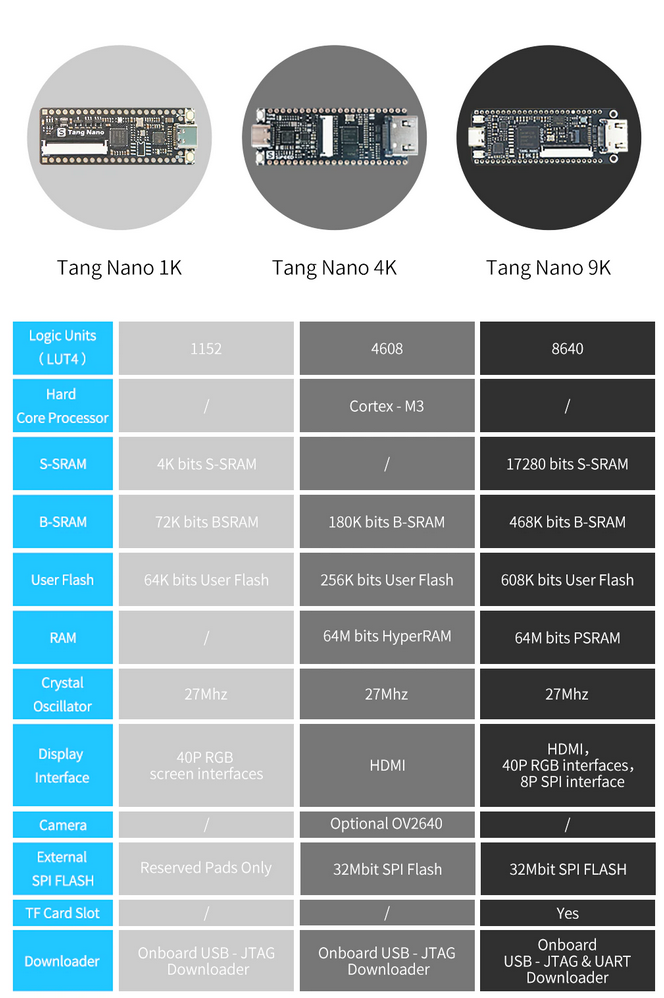

La petite carte, muni d’un littlebee GW1NR-LV9 est tout de même plus grande que les petites sœur. Cette carte est plus «grande» que la 4k mais elle possède autant de PSRAM (64Mbits) et ne possède pas de cœur ARM. La carte possède cependant plus de LUT.

La fiche descriptive d’aliexpress propose un tableau comparatif des trois cartes disponible pour environ $15.

Au branchement, les deux UART du BL702 apparaissent :

[1874406.879770] usb 1-1.1.3: new full-speed USB device number 96 using xhci_hcd

[1874406.980305] usb 1-1.1.3: not running at top speed; connect to a high speed hub

[1874406.981788] usb 1-1.1.3: New USB device found, idVendor=0403, idProduct=6010, bcdDevice= 5.00

[1874406.981794] usb 1-1.1.3: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[1874406.981797] usb 1-1.1.3: Product: JTAG Debugger

[1874406.981800] usb 1-1.1.3: Manufacturer: SIPEED

[1874406.981803] usb 1-1.1.3: SerialNumber: FactoryAIOT Pro

[1874406.991536] ftdi_sio 1-1.1.3:1.0: FTDI USB Serial Device converter detected

[1874406.991586] usb 1-1.1.3: Detected FT2232C

[1874406.992995] usb 1-1.1.3: FTDI USB Serial Device converter now attached to ttyUSB0

[1874406.993170] ftdi_sio 1-1.1.3:1.1: FTDI USB Serial Device converter detected

[1874406.993213] usb 1-1.1.3: Detected FT2232C

[1874406.993538] usb 1-1.1.3: FTDI USB Serial Device converter now attached to ttyUSB1

Et les 6 LED rouges clignotent en même temps.

Le part number du FPGA est GW1NR-LV9QN88PC6/I5 et peut être sélectionné pour la synthèse et le placement-routage avec le logiciel de gowin version 1.9.8.03.

[Article à éditer]

Ressources:

Réception du kit Tang Nano 4K

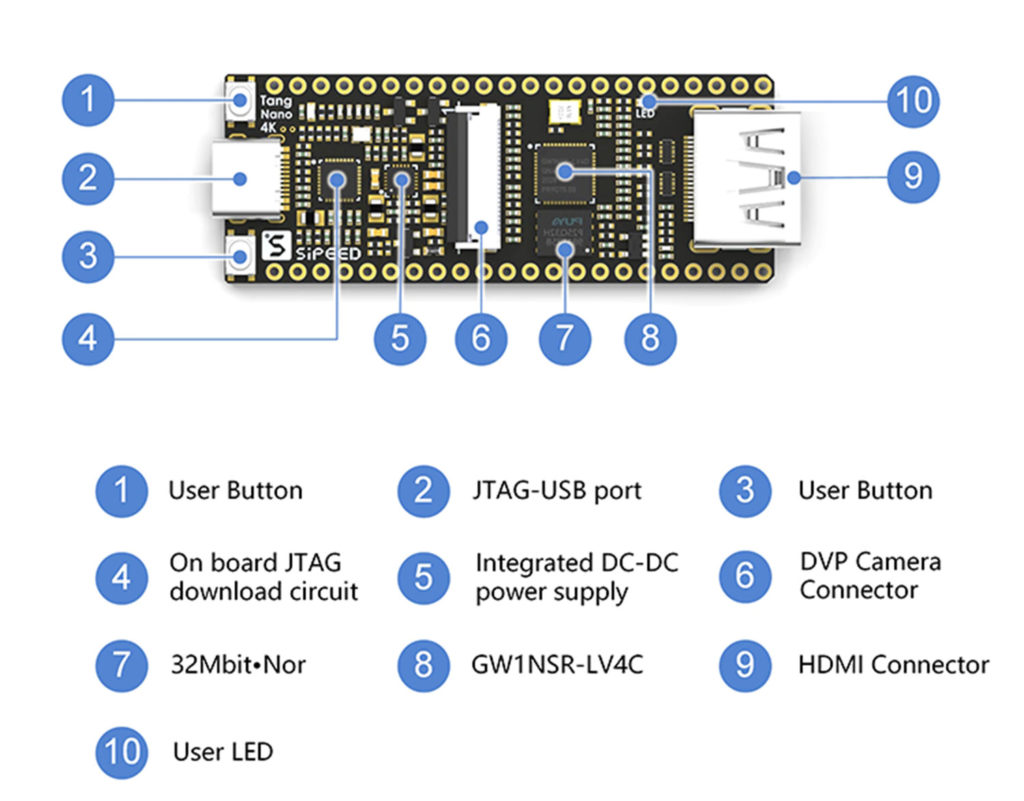

La désormais célèbre société chinoise Sipeed vient de sortir un tout petit kit de développement autour d’un FPGA Gowin et muni d’une sortie HDMI ainsi que d’une entrée caméra : la Tang Nano 4K.

Et non, elle n’est pas compatible avec des écrans HDMI 4K

Il est encore difficile de trouver des informations techniques sur cette carte, pourtant disponible (et rapidement livrée) sur aliexpress. Le wiki officiel est encore intégralement en chinois, mais on trouve le code d’exemple sur github. Le schéma de la carte est dispo sur le site de sipeed ici (ou sur le blog du flf si le firewall chinois fait des caprices

À 18$ il n’était pas question de passer à coté, j’ai donc commandé une version avec caméra OV2640 ainsi qu’une version sans caméra :

Le tout pour une quarantaine d’€.

Branchement

Un câble USB-C est fourni dans la boite, voyons ce qu’il se passe au branchement de la version sans caméra:

sudo dmesg -c

[34644.177355] usb 1-2.1.1: new full-speed USB device number 14 using xhci_hcd

[34644.283502] usb 1-2.1.1: not running at top speed; connect to a high speed hub

[34644.305274] usb 1-2.1.1: New USB device found, idVendor=0403, idProduct=6010, bcdDevice= 5.00

[34644.305288] usb 1-2.1.1: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[34644.305292] usb 1-2.1.1: Product: JTAG Debugger

[34644.305295] usb 1-2.1.1: Manufacturer: SIPEED

[34644.305298] usb 1-2.1.1: SerialNumber: FactoryAIOT Pro

[34644.311295] ftdi_sio 1-2.1.1:1.0: FTDI USB Serial Device converter detected

[34644.311336] usb 1-2.1.1: Detected FT2232C

[34644.316362] usb 1-2.1.1: FTDI USB Serial Device converter now attached to ttyUSB0

[34644.316513] ftdi_sio 1-2.1.1:1.1: FTDI USB Serial Device converter detected

[34644.316548] usb 1-2.1.1: Detected FT2232C

[34644.322352] usb 1-2.1.1: FTDI USB Serial Device converter now attached to ttyUSB1

La version avec caméra donne exactement la même chose.

Le dmesg de Linux laisse apparaître deux interfaces tty. L’une est certainement un convertisseur jtag pour configurer le FPGA et l’autre une interface uart permettant de communiquer avec l’application comme on a pu le voir avec la Tang Nano «classique».

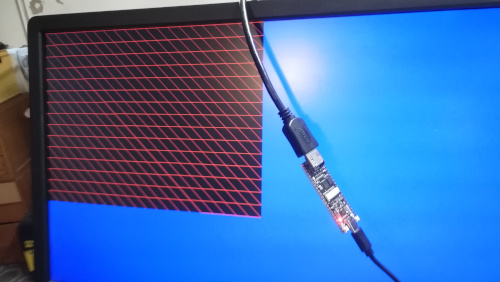

Si l’on branche un écran au HDMI on voit défiler quelques «pattern» avant de s’arrêter sur un écran vert sur fond bleu.

Pour le moment je n’ai pas réussi à obtenir grand chose de ces deux uarts.

Par la suite j’éditerais cet article pour vous parler de la configuration du FPGA.

Synthèse et configuration

Le plus simple pour commencer avec le kit est d’aller voir les deux projets proposés par Sipeed sur github et de les cloner.

$ git clone https://github.com/sipeed/TangNano-4K-example.git

$ cd TangNano-4K-example/Deux projets sont disponible dans ce dépôt, vus de loin l’un est pour faire clignoter une led et l’autre pour l’exemple HDMI programmé par défaut dans l’eeprom du kit :

$ ls

dk_video/ led_test/

Pour se faire la main il est donc naturel de commencer par la led.

Il faut d’abord lancer l’IDE officiel de gowin, comme décrit dans l’article de hackable-32 (le plus compliqué avec l’installation de gowin est d’obtenir la licence, après ça roule). Puis ouvrir le fichier de projet fourni nommé project/led_test.gprj et se trouvant dans le répertoire led_test/projet.

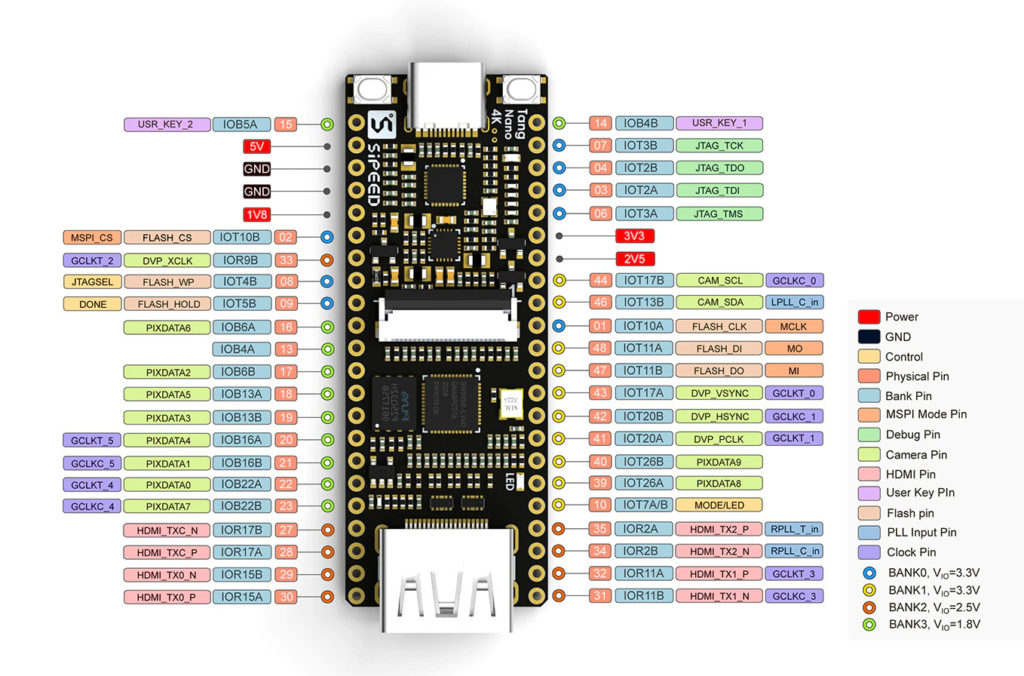

Le FPGA du kit se nomme GW1NSR-LV4CQN48PC7/I6 et le code Verilog de clignotement est le suivant. Quand au pinout le voici au format «cst» ci-dessous :

IO_LOC "led" 10;

IO_PORT "led" PULL_MODE=NONE DRIVE=8;

IO_LOC "sys_rst_n" 15;

IO_PORT "sys_rst_n" PULL_MODE=UP;

IO_LOC "sys_clk" 45;

IO_PORT "sys_clk" PULL_MODE=UP;Le projet est déjà synthétisé, si on souhaite le relancer il suffit de faire un clic-droit «rerun» sur «Synthesize» . Le bitstream est généré au format «fs» et se nomme project/impl/pnr/led_test.fs.

Le kit est désormais reconnu par openFPGALoader:

$ openFPGALoader --detect

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

index 0:

idcode 0x100981b

manufacturer Gowin

family GW1NSR

model GW1NSR-4C

irlength 8

Il suffit donc de programmer le bistrteam (format fs) au moyen de la commande :

$ openFPGALoader led_test/project/impl/pnr/led_test.fs

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse led_test/project/impl/pnr/led_test.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

Flash SRAM: [==================================================] 100.00%

Done

SRAM Flash: Success

Et pour l’écrire dans l’eeprom il suffit d’ajouter l’option -f:

$ openFPGALoader ide/gbhdmi/impl/pnr/gbhdmi.fs -f

write to flash

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse ide/gbhdmi/impl/pnr/gbhdmi.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

erase Flash Done

write Flash: [==================================================] 100.00%

Done

CRC check: Success

Le truc se programme et la led clignote.

Le HDMI

Le deuxième projet proposé dans le dépôt concerne le HDMI. Bon si on regarde le contenu du Top on se rend compte qu’il fait bien plus que le simple HDMI puisqu’il pilote également la ram, la Nor et la caméra.

Le générateur de pattern se charge également de générer les signaux de synchronisation vidéo. Mais ce qui nous intéresse particulièrement c’est le bloc qui pilote le HDMI. Ce bloc se prénomme DVI_TX_top et … il est encrypté

Le bloc est tout de même instanciable au moyen d’une BlackBox chisel. Ce qui permet d’adapter le projet GbVGA en GbHDMI

Pour la vidéo du montage en fonctionnement c’est par là.

La caméra OV2640

Je n’ai pas vu d’exemple de code utilisant la caméra ov2640 avec ce kit pour le moment. Il est probable que ça ne soit pas encore disponible.

Ressources

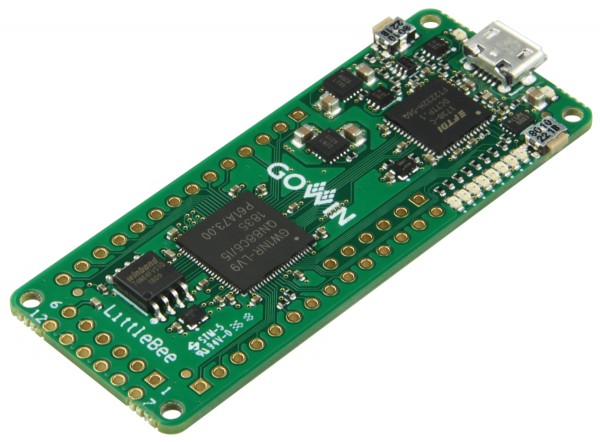

Test d’une carte Gowin avec LiteX

Après avoir déballé le kit gowin proposé par trenz micro. Il faut trouver quelques chose à faire de plus avancé qu’un simple clignotement de LED. Pour le clignotement de LED et la prise en main des outils, le lecteur se référera à l’article Hackable 32.

Pourquoi ne pas tenter le Linux des FPGA, j’ai nommé LiteX (Prononcez Lahïtixe ) ? LiteX est un framework HDL basé sur Migen pour construire des systèmes matériel facilement en python.

LiteX inclut un langage de description matériel, mais également tous les outils permettant de faire des simulations, la synthèses et générer les bitstreams pour la plupart des FPGA du marché. Bien évidement, en ce qui concerne la synthèse et les bitstreams, LiteX pilote les outils propriétaires des constructeurs. Ce pilotage ne pose généralement pas trop de problème, car tous les outils constructeurs proposent des interfaces en ligne de commande.

La carte que nous allons tenter de faire fonctionner avec LiteX est donc la TEC0117-1 produite par Trenz electronic et munie d’un FPGA gowin .

D’après le wiki, la carte n’est pas encore officiellement supporté par LiteX puisqu’elle ne se trouve pas dans la liste du projet LiteX-Boards…

Pas dans le tableau de la documentation du moins, car en fouillant dans le code du projet, il semble qu’il y ait déjà un embryon de quelques chose ici. Voila qui est très engageant pour tester la carte.

Voyons donc voir les étapes nous permettant de construire un système avec LiteX.

Installation de LiteX

Le plus simple pour installer LiteX sur son ordinateur est d’aller suivre le guide officiel d’installation.

$ wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

$ chmod +x litex_setup.py

$ ./litex_setup.py init install --user (--user to install to user directory)Attention, si comme moi vous avez un pc qui commence à prendre sérieusement de l’âge, sachez que le script litex_setup.py va descendre beaucoup de projets annexes de LiteX. Ça va prendre quelques minutes.

On aura besoin également de gcc compilé pour RISC-V :

$ ./litex_setup.py gccIl faudra bien penser à l’exporter à chaque fois qu’on en aura besoin :

$ export PATH=$PATH:$(echo $PWD/riscv64-*/bin/)Construire le système pour TEC0117

Pour construire un système pour la carte il faut ensuite se rendre dans le répertoire contenant la carte puis lancer le script python correspondant:

$ export PATH=$PATH:$(echo $PWD/riscv64-*/bin/)

$ cd litex-boards/litex_boards/targets

$ python3 trenz_tec0117.pyPour synthétiser et générer le bitstream il faut d’abord ajouter le lien vers l’ide (1.9.7 minimum) de gowin :

$ export PATH=$PATH:/opt/gowin/1_9_7/IDE/bin/Puis lancer le build:

$ python litex-boards/litex_boards/targets/trenz_tec0117.py --build

INFO:SoC: __ _ __ _ __

INFO:SoC: / / (_) /____ | |/_/

INFO:SoC: / /__/ / __/ -_)> <

INFO:SoC: /____/_/\__/\__/_/|_|

INFO:SoC: Build your hardware, easily!

INFO:SoC:--------------------------------------------------------------------------------

...

Running timing analysis......

[95%] Timing analysis completed

Bitstream generation in progress......

Bitstream generation completed

Running power analysis......

[100%] Power analysis completed

Generate file "/home/fabienm/myapp/litex/build/trenz_tec0117/gateware/impl/pnr/project.power.html" completed

Generate file "/home/fabienm/myapp/litex/build/trenz_tec0117/gateware/impl/pnr/project.pin.html" completed

Generate file "/home/fabienm/myapp/litex/build/trenz_tec0117/gateware/impl/pnr/project.rpt.html" completed

Generate file "/home/fabienm/myapp/litex/build/trenz_tec0117/gateware/impl/pnr/project.rpt.txt" completed

Generate file "/home/fabienm/myapp/litex/build/trenz_tec0117/gateware/impl/pnr/project.tr.html" completed

Fri Jul 9 13:18:07 2021

Le bitstream généré au format *.fs se trouve ensuite dans le répertoire

./build/trenz_tec0117/gateware/impl/pnr/project.fsOn pourra configurer le FPGA directement avec openFPGALoader :

$ openFPGALoader ./build/trenz_tec0117/gateware/impl/pnr/project.fs

Parse ./build/trenz_tec0117/gateware/impl/pnr/project.fs:

checksum 0x15d3

Done

erase SRAM Done

Flash SRAM: [==================================================] 100.000000%

Done

SRAM Flash: Success

Ou avec la bonne option litex (qui fait appel à openFPGALoader de toute manière):

$ python3 ../litex-boards/litex_boards/targets/trenz_tec0117.py --load

INFO:SoC: __ _ __ _ __

INFO:SoC: / / (_) /____ | |/_/

INFO:SoC: / /__/ / __/ -_)> <

INFO:SoC: /____/_/\__/\__/_/|_|

INFO:SoC: Build your hardware, easily!

INFO:SoC:--------------------------------------------------------------------------------

INFO:SoC:Creating SoC... (2021-07-12 19:05:10)

INFO:SoC:--------------------------------------------------------------------------------

INFO:SoC:FPGA device : GW1NR-LV9QN88C6/I5.

INFO:SoC:System clock: 25.00MHz.

INFO:SoCBusHandler:Creating Bus Handler...

...

INFO:SoC:Initializing ROM rom with contents (Size: 0x51cc).

INFO:SoC:Auto-Resizing ROM rom from 0x6000 to 0x51cc.

Parse /home/user/myapp/litex/myapp/build/trenz_tec0117/gateware/impl/pnr/project.fs:

checksum 0xa3a3

Done

erase SRAM Done

Flash SRAM: [==================================================] 100.000000%

Done

SRAM Flash: Success

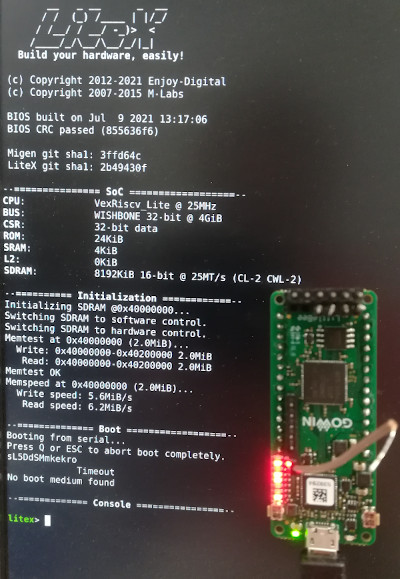

La confirmation de la bonne configuration est donnée par le message de la console, mais également par le chenillard de LED rouge.

Console litex>

Le convertisseur USB-uart de la carte possède deux interfaces ttyUSB, la première vient d’être utilisée par openFPGALoader pour charger le bitstream, la seconde permet de se connecter à la console litex :

$ screen /dev/ttyUSB1 115200

litex> reboot

__ _ __ _ __

/ / (_) /____ | |/_/

/ /__/ / __/ -_)> <

/____/_/\__/\__/_/|_|

Build your hardware, easily!

(c) Copyright 2012-2021 Enjoy-Digital

(c) Copyright 2007-2015 M-Labs

BIOS built on Jul 9 2021 13:17:06

BIOS CRC passed (855636f6)

Migen git sha1: 3ffd64c

LiteX git sha1: 2b49430f

--=============== SoC ==================--

CPU: VexRiscv_Lite @ 25MHz

BUS: WISHBONE 32-bit @ 4GiB

CSR: 32-bit data

ROM: 24KiB

SRAM: 4KiB

L2: 0KiB

SDRAM: 8192KiB 16-bit @ 25MT/s (CL-2 CWL-2)

--========== Initialization ============--

Initializing SDRAM @0x40000000...

Switching SDRAM to software control.

Switching SDRAM to hardware control.

Memtest at 0x40000000 (2.0MiB)...

Write: 0x40000000-0x40200000 2.0MiB

Read: 0x40000000-0x40200000 2.0MiB

Memtest OK

Memspeed at 0x40000000 (2.0MiB)...

Write speed: 5.6MiB/s

Read speed: 6.2MiB/s

--============== Boot ==================--

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

Timeout

No boot medium found

--============= Console ================--

litex>

La commande help nous donnes les commandes disponibles :

litex> help

LiteX BIOS, available commands:

leds - Set Leds value

flush_l2_cache - Flush L2 cache

flush_cpu_dcache - Flush CPU data cache

crc - Compute CRC32 of a part of the address space

ident - Identifier of the system

help - Print this help

serialboot - Boot from Serial (SFL)

reboot - Reboot

boot - Boot from Memory

mem_speed - Test memory speed

mem_test - Test memory access

mem_copy - Copy address space

mem_write - Write address space

mem_read - Read address space

mem_list - List available memory regions

sdram_test - Test SDRAM

Photo traditionnelle

Avec LiteX, une tradition «twitter» veux que l’on fasse une photo du kit démarrant LiteX avec la console démarrée.

Et voila \o/

L’entrée en matière est incroyablement facile et fait honneur au slogan «Build your hardware, easily!».

Nous regarderons dans de futur articles ce que l’on peut faire avec.

Apicula : lancement de la libération du FPGA Gowin GW1N

[Dépèche écrite initialement pour LinuxFR]

Le lecteur assidu de LinuxFr.org sait déjà sans doute ce qu’est un FPGA. Rappelons‑en cependant brièvement la définition.

Les FPGA sont des composants constitués de « champs de portes programmables ». L’idée est de graver un certain nombre d’éléments logiques simples sous forme de matrice et de laisser au développeur le loisir de reconfigurer à l’infini les connexions entre ces portes. Une fois les connexions configurées, on se retrouve avec un composant numérique sur mesure qui ne ressemble à aucun composant disponible chez les fournisseurs classiques. C’est très pratique quand on a besoin d’architectures bâtardes, ou quand justement on développe un composant numérique : ça permet de reconfigurer à l’infini pour déverminer et évaluer les performances.

Pepijn de Vos a effectué un stage pour Symbiotic EDA. Et l’ingénierie inverse du GW1N était son sujet de stage. Il a rendu son rapport avant Noël sur GitHub et a publié le code source du projet Apicula.

Vous voulez en savoir plus, lisez la suite…

Sommaire

- Le Gowin GW1N

- Mais alors, cette LED clignotante, elle vient ?

- Architectures de développement hétéroclites

- C’est encore très expérimental

- Super ! Comment je fais pour contribuer ?

Parlons maintenant du grand drame des FPGA : ils sont complètement verrouillés car, pour reconfigurer ces fameuses connexions, il faut leur téléverser un fichier nommé bitstream qu’aucun constructeur de FPGA ne documente. Ce drame conduit les libristes que nous sommes à se taper des installations d’outils propriétaires particulièrement volumineux (surtout dans le cas de Xilinx et Altera) et pas toujours très stables. Tout ça pour générer le fameux bitstream.

Le format du bitstream n’est pourtant pas chiffré. Depuis plus d’une décennie, on sait qu’il est parfaitement possible d’en faire l’ingénierie inverse. Mais rien n’avait bougé jusqu’en 2015 quand Clifford (qui se prénomme maintenant Claire) Wolf a sorti sa suite open source pour le Lattice iCE40 : IceStorm. Le projet IceStorm avait pour but d’analyser toute la gamme des FPGA iCE40 pour en documenter le format du bitstream. Projet qui a parfaitement abouti et essaimé : toute la gamme des iCE40 est désormais accessible au moyen d’outils open source, ainsi que la gamme des ECP5 avec le Projet Trellis.

Presque tous les modèles de FPGA ont leur projet d’ingénierie inverse aujourd’hui. Tous ne sont pas terminés, loin s’en faut. Néanmoins, quelques‑uns avancent, comme le projet Apicula de Pepijn de Vos ciblant les FPGA du constructeur chinois Gowin. Dire que le projet Apicula est abouti serait un raccourci un peu rapide, il manque encore en effet un certain nombre de blocs à décoder. Cependant, il est possible aujourd’hui de réaliser un projet très simple (UNE LED QUI CLIGNOTE \o/) grâce au travail effectué.

Le Gowin GW1N

Voici l’architecture du GW1N donnée dans la documentation du composant :

Oui, toi aussi, cher lecteur, tu te demandes bien l’intérêt de ce zoom. ;)

On voit différents éléments dans ce schéma, de la mémoire vive, des PLL pour générer les horloges, des multiplieurs câblés (DSP), des blocs d’entrées‑sorties (IOB) et surtout — ce que l’on voit le plus — des CFU (Configurable Function Unit).

Chez Gowin, le CFU est l’élément de base constitué ainsi :

Les deux éléments qui nous intéressent ici sont : la LUT (Look Up Table) et le REG (registre). Ces deux éléments sont la base de la logique synchrone.

Le registre recopie son entrée sur la sortie au front montant de l’horloge, la sortie restant stable le reste du temps.

La LUT, comme son nom anglais l’indique, est une table de vérité, qui, dans le cas de ce petit FPGA, comporte quatre entrées binaires et une sortie. La configuration du FPGA viendra remplir cette table de vérité pour réaliser une fonction logique. Le registre se trouvant derrière se charge ensuite de verrouiller le résultat au rythme de l’horloge.

Si l’on arrive à déchiffrer le bitstream pour pouvoir configurer ces LUT, ces registres ainsi que les blocs d’entrées‑sorties (IOB), alors on a (presque) gagné : on peut réaliser un composant simple mais fonctionnel.

Et c’est ce qu’a réalisé Pepijn de Vos, on peut donc dire qu’il a amorcé la libération du GW1N de Gowin !

Le projet n’est cependant pas terminé, il faut encore déchiffrer les autres blocs pour permettre l’utilisation complète du FPGA. Il faut également réussir à documenter les temps de propagation des signaux entre les différents blocs. L’information de ces temps de propagation permet au logiciel de placement routage (nextpnr, pour ne citer que le plus célèbre en libre) de faire son travail correctement.

Mais alors, cette LED clignotante, elle vient ?

Minute, papillon ! Dans un premier temps, il va falloir trouver une carte électronique munie d’un FPGA de Gowin. Nous allons ensuite nous servir des données déjà produites par le projet Apicula pour faire la synthèse avec Yosys, puis le placement‐routage avec nextpnr.

Pour le moment, deux kits de développement ont été utilisés dans le projet Apicula :

- le kit LittleBee TEC0117, des Allemands de Trenz Electronic (~ 30 €) ;

- le kit Tang Nano, des Chinois de Sipeed (~ 5 €).

Nous allons tester avec le kit allemand TEC0117, mais le Tang Nano ne change pas grand’chose à la procédure (et il est moins cher).

On doit installer :

- Yosys, le logiciel de synthèse Verilog. Pour le détail des dépendances et autres subtilités d’installation, voir le site officiel. Sinon, pour résumer :

git clone https://github.com/YosysHQ/yosys.git

cd yosys make sudo make install- nextpnr, le logiciel de placement routage. Il faut le compiler avec le paramètre «generic». Les deux autres paramètres possible à ma connaissance sont

ice40etecp5(les deux gammes de FPGA vraiment prises en charge par nextpnr) :git clone https://github.com/YosysHQ/nextpnr.git cd nextpnr/ cmake -DARCH=generic . make sudo make installDans mon cas, j’ai dû forcer l’utilisation de Python 3.7 dans le fichierCMakeLists.txt:find_package(PythonInterp 3.7 REQUIRED);pour pouvoir exécuter les scripts en argument avec Python 3.7. - Apicula, dont il faut cloner le dépôt Git :

git clone https://github.com/pepijndevos/apicula.git cd apicula - pour l’instant la « base de données » des éléments trouvés par ingénierie inverse n’est pas « commité » dans le projet Apicula, il faut donc avoir une installation de l’EDI officiel de Gowin ; les scripts du projet Apicula iront fouiller dans les données de l’IDE pour générer un fichier intelligible en JSON et pickle (Python), il n’est cependant pas nécessaire d’avoir la licence ;

- il faut également aller chercher le « pinout » de nos FPGA sur le site officiel de Gowin et le mettre dans son répertoire local nommé

~/Documents/gowinsemi:

Maintenant que nous avons les outils installés, lançons l’exemple générique du projet Apicula :

- d’abord, on génère la base de données des éléments du FPGA :

export GOWINHOME=/chemin/de/linstallation/gowin/IDE/ export DEVICE="GW1NR-9" # TEC0117 python dat19_h4x.py # makes $DEVICE.json python tiled_fuzzer.py # makes $DEVICE.pickle - muni de cette base de données, on peut se lancer dans la synthèse du (pas si) simple porte‑gramme de clignotement de LED donné en Verilog ci‑dessous :

module top; wire clk; (* BEL="R29C29_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(1), .OUTPUT_USED(0)) clk_ibuf (.O(clk)); wire [7:0] leds; (* BEL="R1C8_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led7_obuf (.I(leds[7])); (* BEL="R1C8_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led6_obuf (.I(leds[6])); (* BEL="R1C10_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led5_obuf (.I(leds[5])); (* BEL="R1C10_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led4_obuf (.I(leds[4])); (* BEL="R1C11_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led3_obuf (.I(leds[3])); (* BEL="R1C11_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led2_obuf (.I(leds[2])); (* BEL="R1C12_IOBA", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led1_obuf (.I(leds[1])); (* BEL="R1C12_IOBB", keep *) GENERIC_IOB #(.INPUT_USED(0), .OUTPUT_USED(1)) led0_obuf (.I(leds[0])); reg [25:0] ctr; always @(posedge clk) ctr <= ctr + 1'b1; assign leds = ctr[25:18]; endmoduleUn habitué des LED qui clignotent en Verilog reconnaîtra tout de suite le compteur dans les dernières lignes (always,reg…) mais sera peut‑être perturbé par la déclaration des entrées‑sorties. Il faut juste avoir en tête que le projet n’est pas terminé et qu’il faut se taper le placement‐routage des entrées‑sorties « à la main », d’où les directives(* ... *)et les modulesGENERIC_IOB(). - le script pour la synthèse et le placement routage est donné dans l’exemple :

$ cd generic $ bash simple.sh blinky.v # TEC0117 $ cd .. $ python gowin_pack.py generic/pnrblinky.json $ python gowin_unpack.py pack.fs $ yosys -p "read_verilog -lib +/gowin/cells_sim.v; clean -purge; show" unpack.v - on doit se retrouver avec un bitstream nommé

pack.fsque l’on peut téléverser dans le FPGA au moyen de l’utilitaire libre openFPGALoader maintenu par Trabucayre (Gwenhael Goavec‑Merou) :openFPGALoader -m -b littleBee pack.fs # FOSS programmer Parse pack.fs: Done erase SRAM Done Flash SRAM: [==================================================] 100.000000% Done SRAM Flash: FAILLeFAILest connu et vient d’une sombre histoire de somme de contrôle que openFPGALoader ne sait pas encore calculer et qu’Apicula ne fournit pas. Un ticket est ouvert sur le sujet dans le projet, Trabucayre sera ravi d’accepter des correctifs.

Et les huit LED doivent clignoter. Enfin, disons plutôt qu’elles comptent en binaire. Pour voir la vidéo des LED clignotantes, c’est sur YouTube.

Architectures de développement hétéroclites

Comme nous avons des outils open source, il est possible de développer sur des ordinateurs à base d’architectures différentes de x86. Voici un petit exemple de téléchargement d’un bitstream sur Tang Nano au moyen d’un Raspberry Pi (architecture ARM). Le bitstream en question permet de piloter un écran à cristaux liquides.

Chose impossible à faire avec les Vivado, Diamond et autres Quartus.

C’est encore très expérimental

Comme nous venons de le voir, le projet Apicula est encore très expérimental. Cependant, tous les ingrédients sont là et la preuve de fonctionnement est faite. Donc, à condition de mettre un minimum les mains dans le cambouis, on peut désormais générer des bitstreams pour les GW1Nx avec des outils open source.

Super ! Comment je fais pour contribuer ?

Autant d’enthousiasme fait plaisir à voir. Pour contribuer, le mieux

est d’acquérir l’une des deux cartes citées dans cette dépêche et

d’installer le logiciel officiel de Gowin.

Ensuite, différentes commandes permettant de mettre le pied à l’étrier de l’ingénierie inverse sont données sur le README.md du projet Apicula.

Sinon, n’hésitez pas à laisser une issue sur le projet GitHub ou d’interpeller Pepijn directement sur le « silo social Twitter ». Pepijn est super content de voir des gens s’intéresser au projet et répond très vite.

Aller plus loin

- GitHub du projet (7 clics)

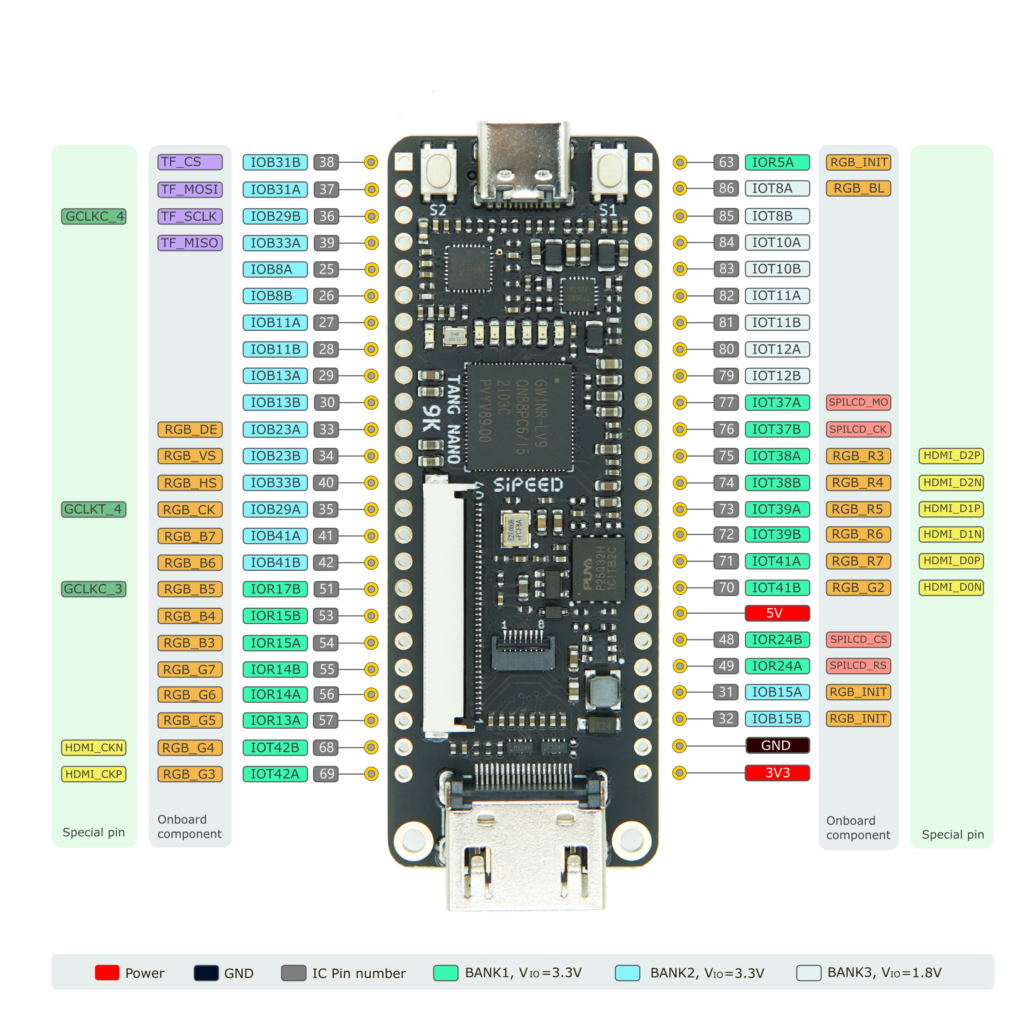

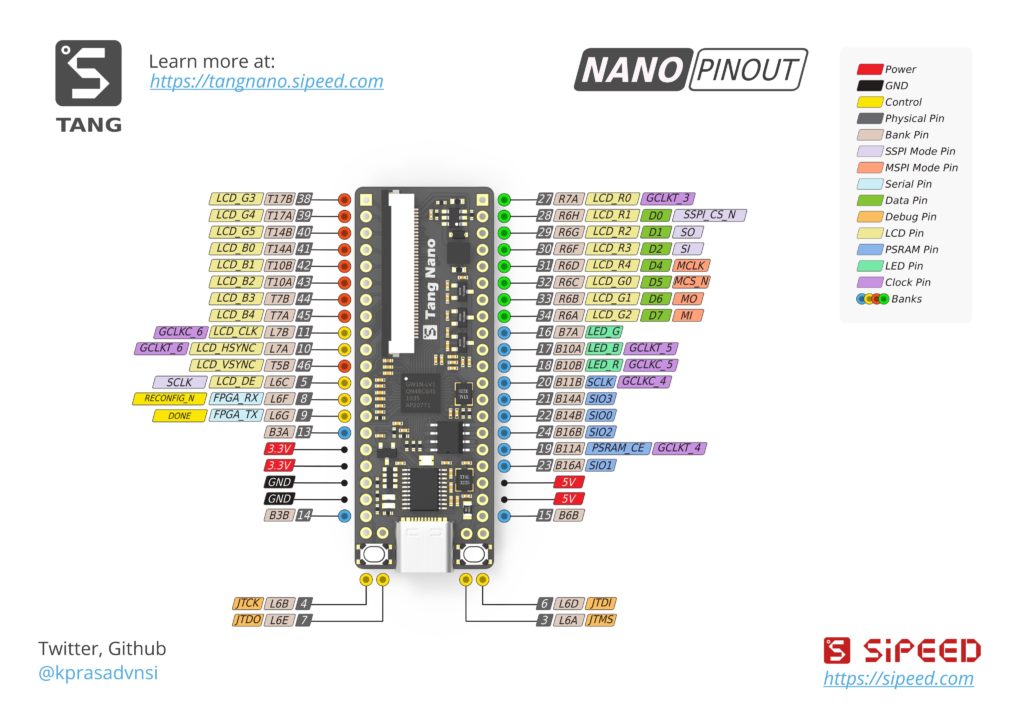

Cool Gowin Tang Nano Pinout

Found on the web:

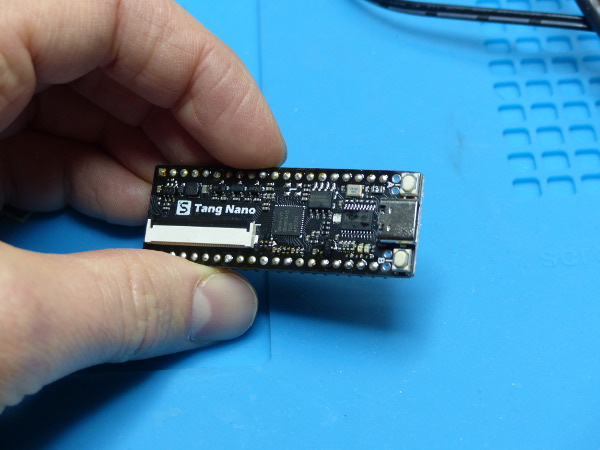

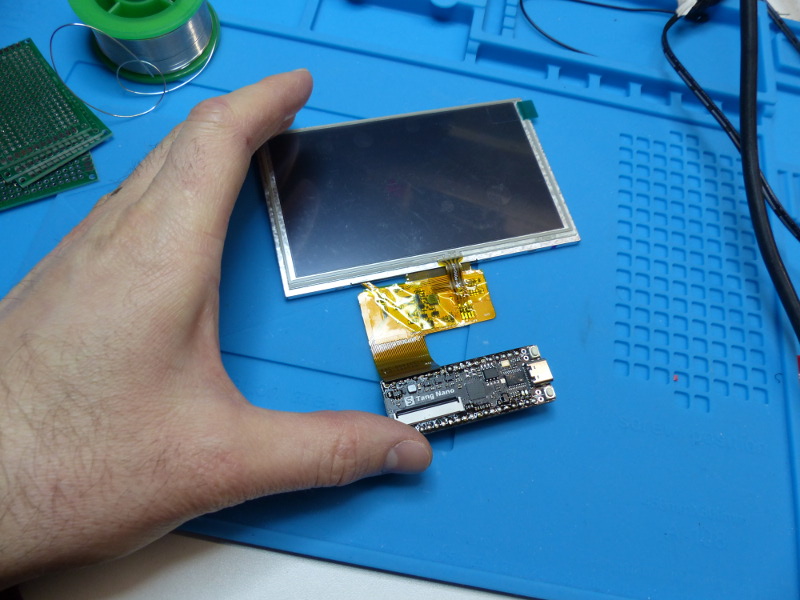

Tang Nano, déballage

Sipeed continue dans sa course à l’échalote des kit FPGA low cost en proposant un kit Gowin à $4.90. Évidemment à ce prix là c’était trop tentant d’en prendre un. Bon en vrai vu que les frais de port ne sont pas négligeable j’ai également pris l’écran proposé et je m’en suis finalement sortie pour une vingtaine d’€. Ce qui reste néanmoins raisonnable.

Le kit est fourni avec des headers males (pattes) non soudés. Ils ne sont pas nécessaire pour faire clignoter la LED ou pour jouer avec l’écran, mais c’est quand même utile.

Premier boulot en recevant le truc donc : souder les headers.

Le FPGA soudé sur la carte est un GW1N-LV1, assez petit donc, mais il reste raisonnable puisque de la même taille que le ice40 soudé sur le icestick. C’est d’ailleurs le kit utilisé actuellement par Pepijn de Vos son projet d’ingénierie inverse nommé Apicula (mais chuuut le projet n’est pas encore public !).

Le branchement se fait au moyen d’un câble USB-C non fourni. Au premier branchement, la LED rouge qui semble être celle de l’alimentation s’allume et la led RGB du centre se met à clignoter en allumant les trois couleurs à la suite.

Les messages noyau m’affichent le traditionnel double tty typique d’un convertisseur USB-Série habituel (CH552T, un microcontrôleur chinois):

$ sudo dmesg -c

[365812.686837] usb 3-2: new full-speed USB device number 25 using xhci_hcd

[365812.838484] usb 3-2: New USB device found, idVendor=0403, idProduct=6010, bcdDevice= 5.00

[365812.838490] usb 3-2: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[365812.838492] usb 3-2: Product: Sipeed-Debug

[365812.838494] usb 3-2: Manufacturer: Kongou Hikari

[365812.838496] usb 3-2: SerialNumber: 85522A1A47

[365812.840468] ftdi_sio 3-2:1.0: FTDI USB Serial Device converter detected

[365812.840534] usb 3-2: Detected FT2232C

[365812.841192] usb 3-2: FTDI USB Serial Device converter now attached to ttyUSB0

[365812.841373] ftdi_sio 3-2:1.1: FTDI USB Serial Device converter detected

[365812.841427] usb 3-2: Detected FT2232C

[365812.841727] usb 3-2: FTDI USB Serial Device converter now attached to ttyUSB1

On remarquera que cette fois le numéro de série n’est pas en chinois

La connexion au ttyUSB0 (en 115200) fournie un echo du clavier un peu bizarre :

�n�a�u�r�s�i�t�e�n�a�s�u�t�i�e�n�a�s�u�t�i�e�n�s�a�u�t�i�e�n�r�a�s�u�t�i�e�n�r�s�a�u�t�i�e�n�r�s�a�t�u�i�eEt le ttyUSB1 semble ne pas «fonctionner».

Il est fort probable que le kit soit entièrement utilisable avec des logiciels libre à Noël lors de la grand messe allemande : le Chaos Communication Congress à Liepnitz.

Pour le moment nous allons nous contenter de l’IDE chinois fourni, que j’avais déjà installé pour le little bee. Pour le code, il y a des exemples fournis sur le github de sipeed. Pour la documentation c’est par ici. Et comme d’habitude avec les trucs chinois, quand la doc en anglais semble trop limitée, ne pas hésiter à aller faire un tour sur la version chinoise à coup de google traduction.

Trucs:

Si le floorplanning ne veut pas se lancer c’est qu’il faut bien configurer sa variable LD_LIBRARY_PATH avant de lancer l’appli:

$ export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:/home/flf/myapp/gowin/IDE/lib

$ ./gw_ide -guiRessources

– Nano board pinout (blog)

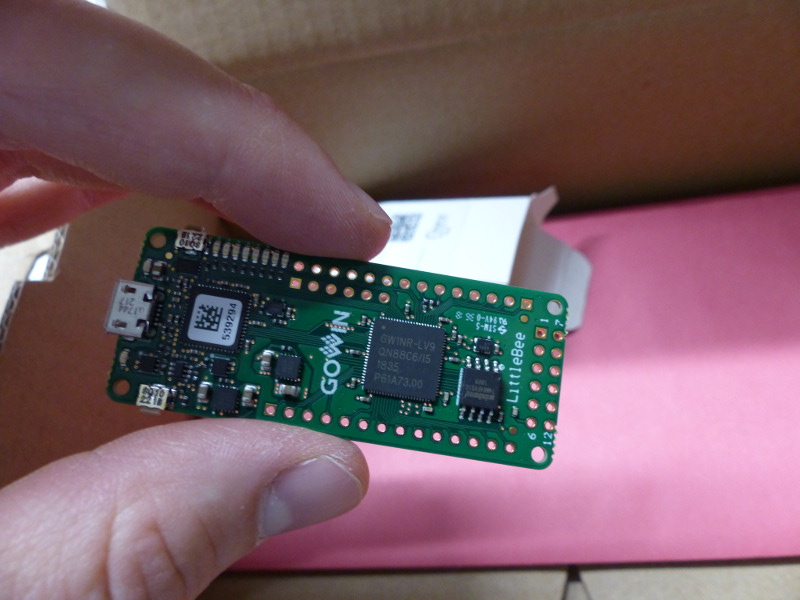

Le point Gowin

Oui je sais c’est nul

Je viens donc de recevoir ma carte petite abeille (littlebee) munie d’un FPGA du chinois GOWIN.

La carte produite et vendue par la société allemande Trenz Electronic permet de se faire la main avec le composant pour moins de 40€ (un peu plus avec les frais de ports UPS …).

Branchement

Au branchement à la sortie du carton les huit leds rouge s’allument ainsi qu’une led verte que je suppose de «power».

Les messages noyau nous donnent deux ports séries ttyUSBx :

$ dmesg

[630417.919258] usb 3-1: new high-speed USB device number 35 using xhci_hcd

[630418.059577] usb 3-1: New USB device found, idVendor=0403, idProduct=6010

[630418.059581] usb 3-1: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[630418.059583] usb 3-1: Product: Dual RS232-HS

[630418.059584] usb 3-1: Manufacturer: FTDI

[630418.060116] ftdi_sio 3-1:1.0: FTDI USB Serial Device converter detected

[630418.060155] usb 3-1: Detected FT2232H

[630418.060352] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB0

[630418.060499] ftdi_sio 3-1:1.1: FTDI USB Serial Device converter detected

[630418.060528] usb 3-1: Detected FT2232H

[630418.060648] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB1

Si on se connecte au port série ttyUSB1 on obtient un affichage de la résolution du problème des philosophes.

Philosopher 0 [P: 3] THINKING [ 750 ms ]

Philosopher 1 [P: 2] HOLDING ONE FORK

Philosopher 2 [P: 1] EATING [ 450 ms ]

Philosopher 3 [P: 0] STARVING nabled

Philosopher 4 [C:-1] HOLDING ONE FORK get back,

Philosopher 5 [C:-2] EATING [ 375 ms ]

Il est probable que nous ayons ici un RISC-V dans le tiroir.

La connexion d’un terminal sur le port ttyUSB0 ne donne rien par contre.

IDE

Voila pour le déballage, maintenant il va falloir installer les outils pour faire clignoter ces leds !

[To Be Edited …]