[depêche parue initialement sur LinuxFR]

CLEAR est un microcontrôleur RISC-V (VexRISCV) muni d’un eFPGA gravé en 130 nm et produit avec le programme chipignite de la société de production d’ASIC Efabless. La totalité du « dossier de fabrication » du composant est publiée en open source.

Sommaire

- openFPGA : le générateur de FPGA

- Caravel : embarquez votre composant avec un processeur RISC-V

- Chipignite : les ASIC pour tous

- Sky130 : le « kit ASIC » (pdk) libéré

- Open MPW shuttle : les ASIC open source gratuits de google

- La production de CLEAR en financement participatif

Un FPGA est un type particulier de composant électronique. Il peut être vu comme un « kit » de portes logiques avec des connexions reconfigurables à l’infini. Le tout est assemblé dans un même composant. Les constructeurs de FPGA gardent jalousement secrète une partie de l’architecture de leurs composants et ne fournissent même pas la documentation permettant de les configurer. Il est nécessaire de passer par leurs logiciels (binaires) pour générer le fichier de configuration appelé bitstream.

La conception et la fabrication d’un FPGA passent par les mêmes procédés que pour n’importe quel composant électronique numérique (processeur, périphérique, microprocesseur) : on part d’un modèle numérique du composant que l’on va transformer en un dessin « 3D » du circuit final appelé GDSII. Toute cette chaîne de fabrication utilise un tas de formats et de standards jalousement gardés secrets par les différents acteurs de cette industrie. Il est évident que les fabricants de FPGA gardent secret ces « dossiers de fabrication ».

Il y a quelques années, Claire Clifford libérait le format des bitstreams de configuration du FPGA ice40 par rétro-ingénierie avec le projet Icestorm. D’autres FPGA ont ensuite été libérés par ingénierie inverse, sans soutien des différents constructeurs.

Un pas de plus dans la libération des FPGA a été franchi avec la production du EOS S3 de la société QuickLogic. QuickLogic a publié le format du bitstream de la partie FPGA (eFPGA) de son composant et supporte officiellement les outils opensource.

Avec le CLEAR, on passe à une toute autre échelle de libération pour les FPGA. En effet — cette fois — c’est la totalité du « dossier de fabrication » qui est libéré. Commençons par le cœur du composant : openFPGA.

openFPGA : le générateur de FPGA

L’architecture utilisée dans le CLEAR est celle du projet openFPGA. Le projet propose de générer une structure de FPGA « prête à graver » à partir d’un simple fichier de configuration de l’architecture voulue. L’objectif étant de réduire le temps de développement d’un FPGA à 24 heures, au lieu des mois habituels.

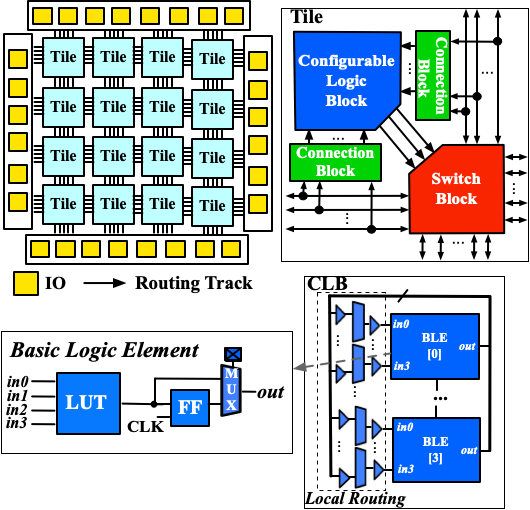

L’architecture du eFPGA est constituée de 8 × 8 = 64 CLB. Chaque CLB contient quatre Blocs Logique Élémentaire (BLE) avec à chaque fois :

Ce type d’architecture se retrouve dans tous les FPGA avec une variation sur le nombre d’entrées de la LUT. Cela nous permet de comparer les FPGA en termes de nombre de LUT.

Avec le CLEAR nous avons donc un eFPGA de 256 LUT. Pour comparer on peut parler du EOS S3 qui possède 891 LUT ou du ICE40 dont la gamme débute à 384 LUT et monte jusqu’à environ 8000 LUT.

On parle donc d’un tout petit eFPGA. Avec une architecture de FPGA open source, il est plus évident de développer des outils libres pour travailler sur ces FPGA. L’outil de référence pour configurer les FPGA générés avec openFPGA est issu majoritairement du projet VTR (Verilog To Routing).

La partie FPGA ainsi générée est prête à être intégrée dans la caravelle.

Caravel : embarquez votre composant avec un processeur RISC-V

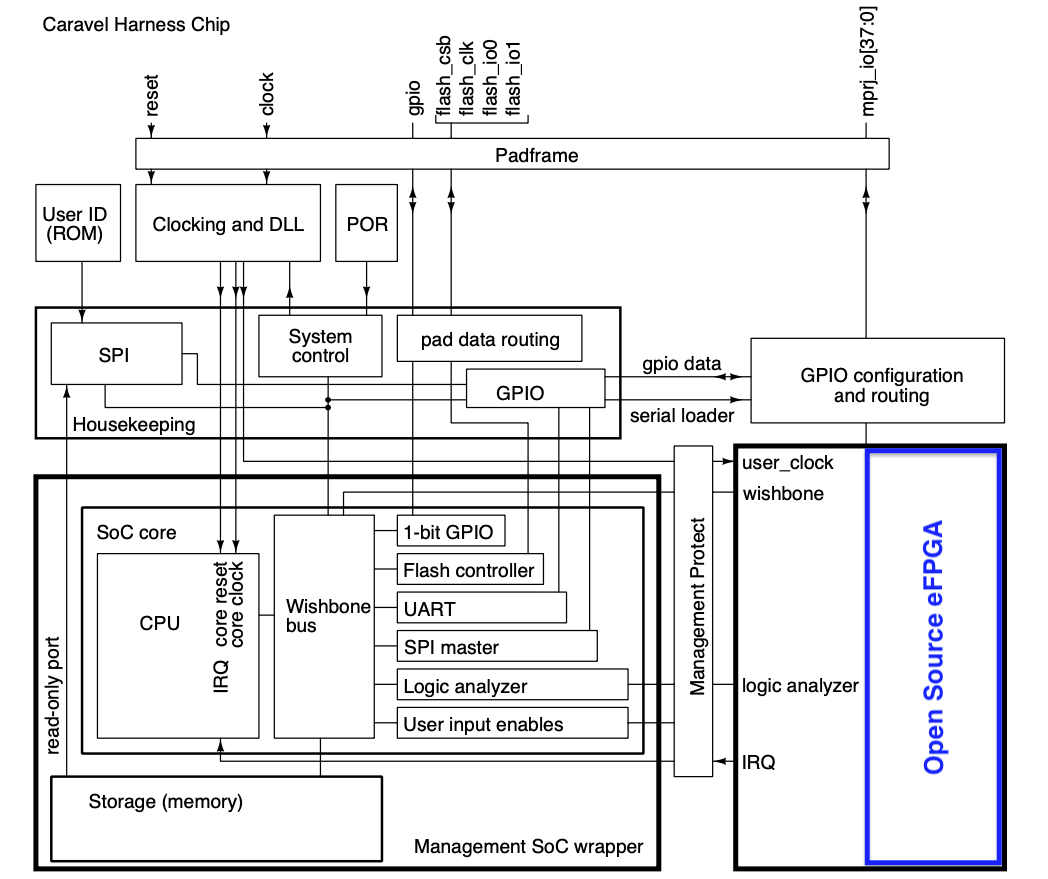

La lectrice ou le lecteur aura certainement remarqué que le titre de la dépêche ne parle pas de FPGA mais de eFPGA. e qui signifie simplement « embedded ». Le FPGA généré est embarqué dans un composant plus gros muni d’un microprocesseur 32 bits nommé VexRisc qui est openSource lui aussi.

Ce processeur — développé par Charles Papon avec le langage HDL SpinalHDL — est la base du SoC Caravel développé par la société eFabless et open source lui aussi.

L’objectif de Caravel est de proposer un SoC complet avec le CPU, quelques périphériques (UART, SPI, GPIO, RAM…) et une zone libre pour y graver un composant de son cru. Toute la partie « outils de déverminage » est ainsi standardisée avec tous les signaux nécessaires au bon fonctionnement du projet cible.

Avec cet outil libre, efabless veut démocratiser la fabrication de composant électronique et la rendre accessible aux petites PME, voire aux particuliers.

Ce kit de développement est proposé par la société efabless avec son programme chipignite.

Chipignite : les ASIC pour tous

Avec le programme Chipignite d’efabless, il est en effet possible de faire produire 100 composants (ou 300 selon le boîtier choisi) pour moins de 10 000 $ gravé en 130 nm.

À ce prix-là, on a tous les outils de développement à disposition ainsi que les bibliothèques du kit de développement (PDK) en 130 nm du fabricant, sans avoir à signer d’accord de non divulgation (NDA) pour lire l’accord de non divulgation à signer.

Comme le nom de la société le laisse entendre, efabless ne possède pas d’usine de fabrication. Elle se contente de réserver des slots (shuttle) de fabrication dans l’usine américaine skywater.

Sky130 : le « kit ASIC » (pdk) libéré

Skywater est un petit fabricant de composants électroniques américain. C’est une ancienne usine de Cypress qui a pris son indépendance.

Cette entreprise fabrique des semi-conducteurs à des niveaux de gravure qui sont aujourd’hui considérés comme largement amortis. Le 130 nm par exemple est la finesse de gravure utilisée il y a 20 ans pour les processeurs Pentium III ou pour le processeur de la Gamecube.

Pour faire produire un composant électronique, il faut fournir un fichier de fabrication au format GDSII. Qui est un format ouvert de description des différentes couches de dopage et de connexions métal du composant.

Mais pour générer ce GDSII, l’entreprise qui conçoit des composants a besoin de connaître les propriétés du substrat fabriqué. Il faut un modèle pour simuler les composants que l’on « dessine ».

À partir de ce modèle il est possible d’établir une bibliothèque de composants comme des transistors, bascules, mémoire et autres.

Toutes ces informations sont rassemblées dans ce qu’on appelle un PDK (Process Design Kit). Le PDK est intimement lié au fabricant et au process de fabrication. Sans lui, impossible de concevoir et générer le GDSII, malgré la disponibilité de nombreux (et vieux) logiciels libres dans le domaine.

Jusqu’à l’année dernière, il n’existait pas de PDK « ouvert » : impossible pour une petite entreprise d’y avoir accès sans payer des sommes folles en licences de développement. Sans compter sur les accords de non divulgation qui rendaient impossible la diffusion du GDSII en dehors de la production.

Pour dynamiser sa production, Skywater a donc décidé, avec l’aide de Google, de libérer son PDK pour la finesse de gravure de 130 nm. Le PDK se nomme Sky130 et est disponible à tous sous licence Apache 2.0 sur github.

Open MPW shuttle : les ASIC open source gratuits de google

10 000 $ ça ne se trouve pas sous le sabot d’un cheval. Il y a intérêt d’avoir un projet un peu plus solide qu’un simple TapTempo. Une PME peut prendre des risques avec cette somme mais de manière mesurée.

Pour favoriser l’émergence d’une communauté open source dans le développement matériel et pour encourager les développeuses et développeurs à prendre des risques et innover, Google a décidé de financer des productions de composants tous les six mois.

Pour être dans la « navette » nommée Open MPW shuttle il faut proposer un composant totalement open source et publier tous les scripts permettant de re-générer le GDSII.

Si le projet est jugé intéressant, efabless fera fabriquer une série de composants gratuitement.

Et c’est ce qui s’est passé avec le projet Caravel-OpenFPGA-EF qui a été produit dans la première navette MPW-1.

OpenFPGA a également été utilisé dans la seconde navette MPW-2 avec le projet SOFA.

Il y a d’autre projet de eFPGA dans les navettes, mais OpenFPGA semble être le plus utilisé et le plus facile d’accès.

La production de CLEAR en financement participatif

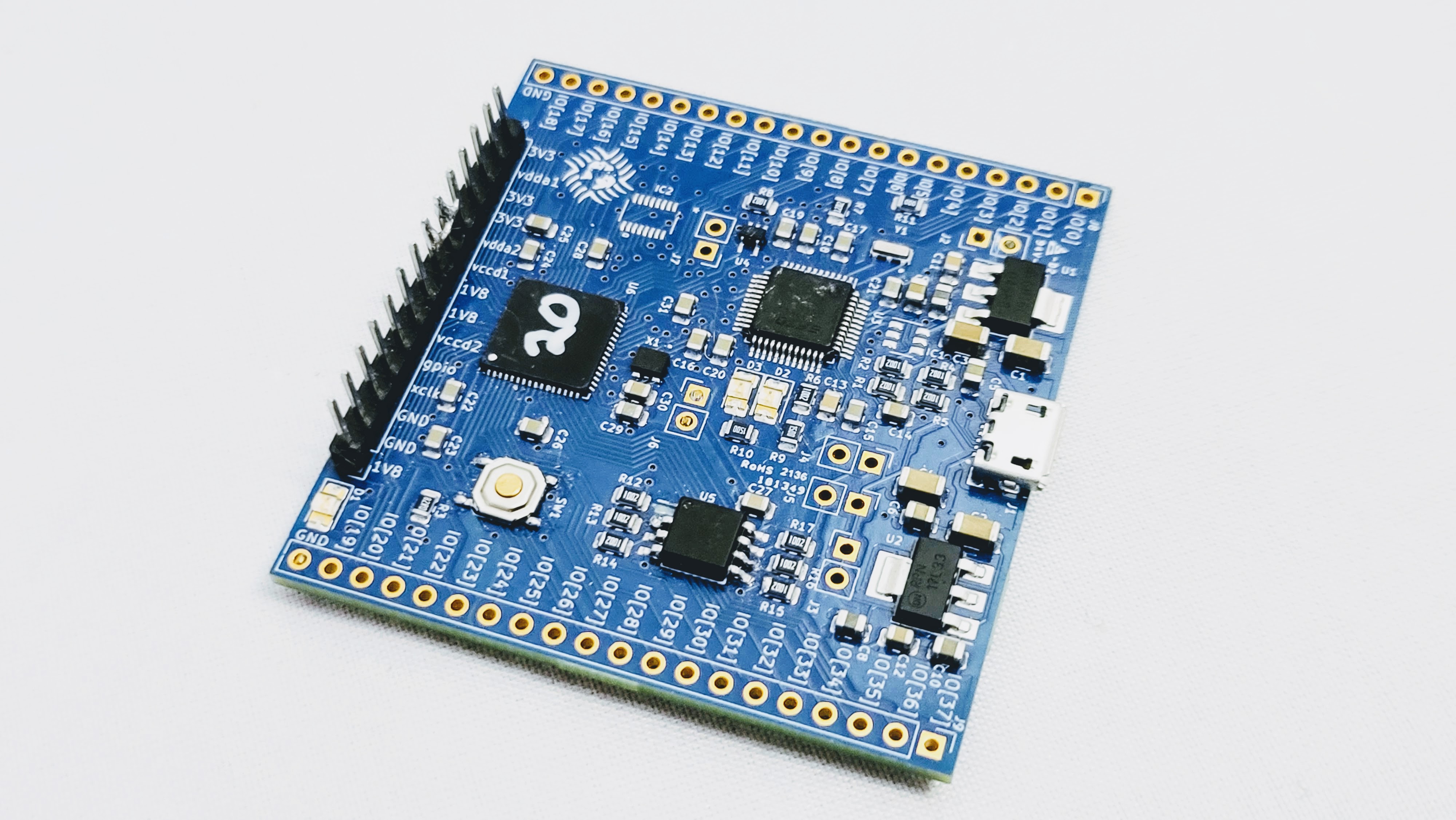

Pour montrer la possibilité de produire un eFPGA open source un financement participatif a été lancé sur le site groupgets.

Moyennant 75 $ (plus les frais de port plus certainement la douane) il est possible d’acquérir ce microcontrôleur soudé sur une carte de développement.

Une fois la levée de fonds bouclée, le projet sera embarqué dans la navette 2204C pour une production prévue en avril 2022.

Bien sûr, une carte de développement à ce prix pour un eFPGA aussi petit peut sembler inintéressante. Il faut plutôt le voir comme une somme accessible à (presque) tout le monde pour entrer dans le monde du silicium et des FPGA opensource. C’est, en tout cas la preuve, qu’il est possible de produire un FPGA (+ microcontrôleur) intégralement open source à des tarifs raisonnables.